問題の定式化

あなたはオフィス用のソフトドリンクマシンを設計するように説得されました。ドリンクは組合によって部分的にカバーされているので、5ルーブルしかかかりません。マシンは、1、2、5ルーブルの硬貨を受け入れます。顧客が必要な金額を支払うとすぐに、マシンが飲み物を分配し、釣銭を返します。清涼飲料の自動販売機のステートマシンを設計します。マシンの入力は、1、2、および5ルーブルです。つまり、これらのコインのどれが挿入されます。

クロックごとに1つのコインのみが挿入されると仮定します。マシンには出力があります:ソーダを注ぐ、1ルーブルを返す、2ルーブルを返す、2ルーブルの場合は2を返します。自動販売機で5ルーブル(またはそれ以上)が収集されるとすぐに、信号 "FILL GASING"と、対応する変更を返すための信号が設定されます。その後、マシンは再びコインを受け入れる準備ができているはずです。

理論

有限状態機械または有限状態機械(FSM)は、大部分のデジタル回路を表す同期シーケンシャル回路のクラスに属します。これは、プロジェクトを実装する方法です(少なくとも最初は)。この方法は、回路の再現性と検証を提供し、さまざまな回路要素の遅延比に依存しません。同期シーケンシャル回路を構築するための規則では、回路の要素が次の条件を満たす場合、回路は同期シーケンシャル回路であると規定されています。

- 各回路要素は、レジスタまたは組み合わせ回路です。

- 少なくとも1つのスキーマ要素がレジスターです。

- すべてのレジスタは、単一のクロック信号でクロックされます。

- 各循環パスには、少なくとも1つのレジスタが含まれます。

状態機械にはいくつかの状態があり、それらはレジスターに保管されます。クロック信号が到着すると、ステートマシンはその状態を変更できます。状態がどの程度正確に変化するかは、入力信号と現在の状態によって異なります。最も単純なケースでは、入力信号がまったくない場合があるため、分周器が機能します。有限状態機械には主に2つのクラスがあります。出力信号がオートマトンの現在の状態のみに依存するムーアオートマトンと、出力信号が現在の状態と入力信号に依存するミーリーオートマトンです。原則として、任意の有限状態機械は、ムーアスキームとマイリースキームの両方に従って実装できます。両者の違いは、ムーアオートマトンがより多くの状態を持ち、Milyオートマトンの1クロック遅れることです。ソーダマシン回路には、マイル回路を使用します。状態機械を述べましょう:

| シンボル | 説明 |

|---|---|

| S 0 | 初期状態は、0ルーブルの累積額。 |

| S 1 | 1回の摩擦の累積量。 |

| S 2 | 2ルーブルを蓄積した。 |

| S 3 | 3ルーブルを蓄積した。 |

| S 4 | 4ルーブルを蓄積した。 |

入力信号は2ビットバスで、コインの金種は次のようにコーディングされています。

| シンボル | 値 | 説明 |

|---|---|---|

| 私1 | 01 | 1 RUB |

| 私2 | 十 | RUB 2 |

| 私5 | 十一 | RUB 5 |

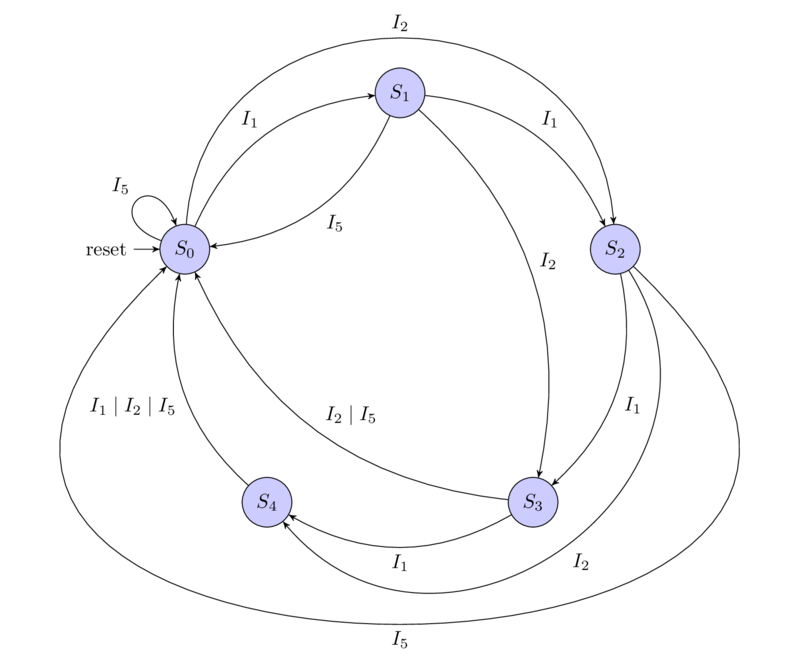

オートマトンの状態図を描画します(Milyオートマトンの状態図では、状態遷移の矢印に出力信号を示す必要があります。図が乱雑にならないようにこれを行わないでください。すべての出力信号は下の表に描かれます):

状態と出力信号の変化の表を書き込みます:

| 州 | 入力信号 | |||||

|---|---|---|---|---|---|---|

| S | S' | insert | pour_water | C 1 . change1 | 2 . change2 | 2 2 . change22 |

| S0 | S1 | I1 | 0 | 0 | 0 | 0 |

| S0 | S2 | I2 | 0 | 0 | 0 | 0 |

| S0 | S0 | I5 | 1 | 0 | 0 | 0 |

| S1 | S2 | I1 | 0 | 0 | 0 | 0 |

| S1 | S3 | I2 | 0 | 0 | 0 | 0 |

| S1 | S0 | I5 | 1 | 1 | 0 | 0 |

| S2 | S3 | I1 | 0 | 0 | 0 | 0 |

| S2 | S4 | I2 | 0 | 0 | 0 | 0 |

| S2 | S0 | I5 | 1 | 0 | 1 | 0 |

| S3 | S4 | I1 | 0 | 0 | 0 | 0 |

| S3 | S0 | I2 | 1 | 0 | 0 | 0 |

| S3 | S0 | I5 | 1 | 1 | 1 | 0 |

| S4 | S0 | I1 | 1 | 0 | 0 | 0 |

| S4 | S0 | I2 | 1 | 1 | 0 | 0 |

| S4 | S0 | I5 | 1 | 0 | 0 | 1 |

Quartus Prime

Quartusには無料のLiteエディションがあり、プロフェッショナルエディションと比較していくつかの制限があります。主な制限は、プロジェクトシミュレーションのソースコードが10,000行を超えないことです。登録後、リンクからダウンロードできます。この記事の執筆時点での最新バージョンは19.1でした。このバージョンでの作業に基づいて、記事を書きました。 Lite Edition、バージョン19.1、Windowsオペレーティングシステムを選択します(LinuxにはQuartusバージョンがあり、正常に動作します。32ビットで、古いバージョンのフォントマッピングライブラリを使用するModelSimで問題が発生するため、最初にWindowsバージョンを使用することをお勧めします。 )、[結合ファイル]タブを選択します。ダウンロード用のアーカイブのサイズは非常に大きいです-5.6 Gb、これを覚えておいてください。ダウンロードしたアーカイブを展開して実行しますsetup.bat。インストールは標準的な方法で行われ、コンポーネントのデフォルトの選択を使用します。

プロジェクトの作成

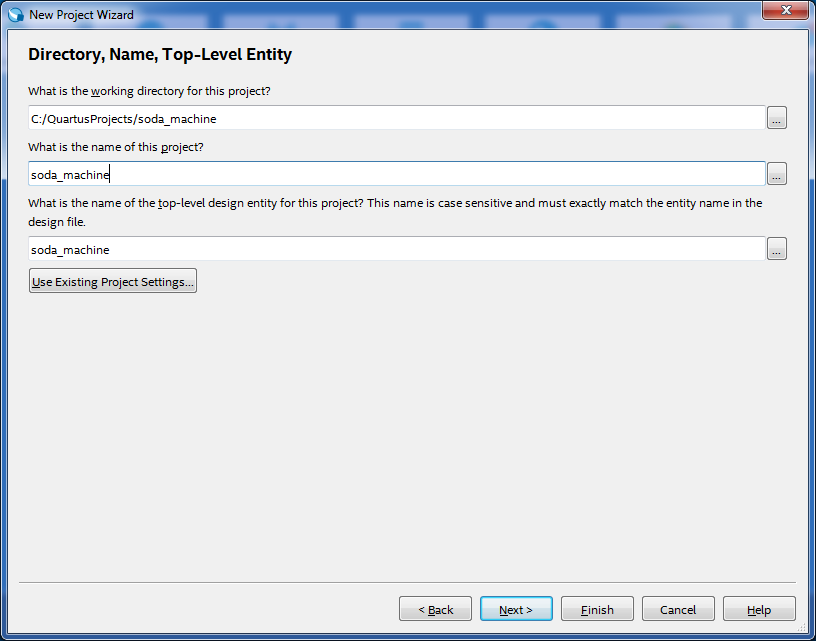

新しいプロジェクトを作成するには、[ ファイル]→[プロジェクトウィザードによる新規作成...]を選択します。最初のウィザードウィンドウは情報を提供するものであり、次へをクリックし、2番目のウィンドウで、プロジェクトを配置する場所、その名前「soda_machine」、およびトップレベルの設計要素「soda_machine」を図のように

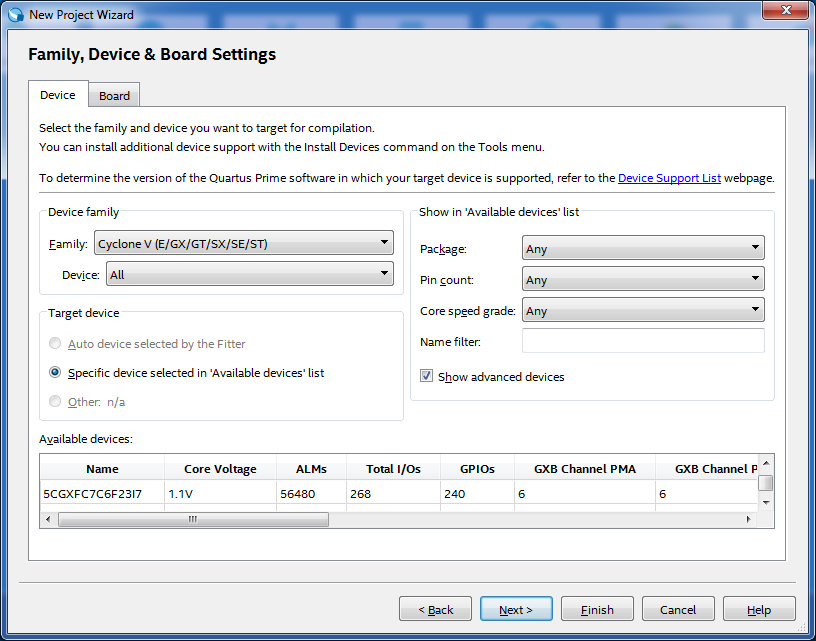

選択します。次のウィンドウで「空のプロジェクト」を選択します。ファイルを追加するウィンドウ「ファイルを追加」、何も追加しません。「ファミリ、デバイス、ボード設定」のデバイス選択ウィンドウは実際のプロジェクトにとって非常に重要ですが、私たちのプロジェクトは教育的であり、実際のプロジェクトとはかけ離れている

ため、図のようにここではデフォルト設定のままにします。他のツールの設定を選択するためのウィンドウ「EDAツールの設定」、使用するプロジェクトをシミュレートすることを選択し、「ModelSimのアルテラの」と「システムのVerilog HDL」形式を絵のように:

最後の情報ウィンドウ「概要」をクリックし、完了を。

ソースコードを書く

ソースコードを含む2つのメインファイルがあります。これはsoda_machineモジュール自体とそのテストベンチです。これらのファイルはどちらも、硬貨の種類をエンコードする方法を記述するinsert_typeデータ型を使用し、それを別のファイルに分離することは論理的です。ただし、QuartusおよびModelSimのコンパイル機能に関連するいくつかの問題があります。 Quartusはすべてのソースファイルを1回のパスでコンパイルし、ModelSimは各ファイルを個別にコンパイルするため、Quartusをコンパイルするときにinsert_type型の再定義がないため、マクロプロセッサディレクティブに基づいてC / C ++インクルードガードの手法を使用しました。また、ModelSimのためにことを確認するためにinsert_typeがで使用soda_machineのモジュールそして、テストベンチでは、同じように、その説明をsoda_machine_typesパッケージ内に配置します。これらの要件を考慮すると、soda_machine_types.svファイルは次のようになります。

soda_machine_types.sv

`ifndef soda_machine_types_sv_quard

package soda_machine_types;

typedef enum logic [1:0] {I1=2'b01, I2=2'b10, I5=2'b11} insert_type;

endpackage

`define soda_machine_types_sv_quard

`endif

これで、soda_machineモジュール自体がsoda_machine.svファイルに配置されます。

soda_machine.sv

`include "soda_machine_types.sv"

import soda_machine_types::*;

module soda_machine(

input logic clk, // Clock

input logic reset, // Active high level

input insert_type insert,

output logic pour_water,

output logic change1,

output logic change2,

output logic change22);

typedef enum logic [2:0] {S0, S1, S2, S3, S4} state_type;

(* syn_encoding = "default" *) state_type state, nextstate;

//

always_ff @(posedge clk, posedge reset)

if (reset)

state <= S0;

else

state <= nextstate;

//

always_comb

case (state)

S0:

case (insert)

I1:

nextstate = S1;

I2:

nextstate = S2;

I5:

nextstate = S0;

endcase

S1:

case (insert)

I1:

nextstate = S2;

I2:

nextstate = S3;

I5:

nextstate = S0;

endcase

S2:

case (insert)

I1:

nextstate = S3;

I2:

nextstate = S4;

I5:

nextstate = S0;

endcase

S3:

if (insert == I1)

nextstate = S4;

else

nextstate = S0;

S4:

nextstate = S0;

endcase

//

assign pour_water = (state == S4) | (insert == I5) | (state == S3) & (insert == I2);

assign change1 = (state == S1) & (insert == I5) | (state == S3) & (insert == I5) | (state == S4) & (insert == I2);

assign change2 = (state == S2) & (insert == I5) | (state == S3) & (insert == I5);

assign change22 = (state == S4) & (insert == I5);

endmodule

ステートマシンの状態がどのようにエンコードされるかは、Quartusに任せました。エンコーディングの方法を示すために、属性(* syn_encoding = "default" *)が使用されます。他のエンコーディングオプションは、ここで確認できます。

実際のプロジェクトでは、Milesマシンの組み合わせロジックの出力信号をレジスターに格納し、レジスターの出力からFPGA出力に供給する必要があることに注意してください。メタステーブル状態に陥らないようにするには、シンクロナイザーを使用して入力信号をクロック周波数と同期させる必要があります。

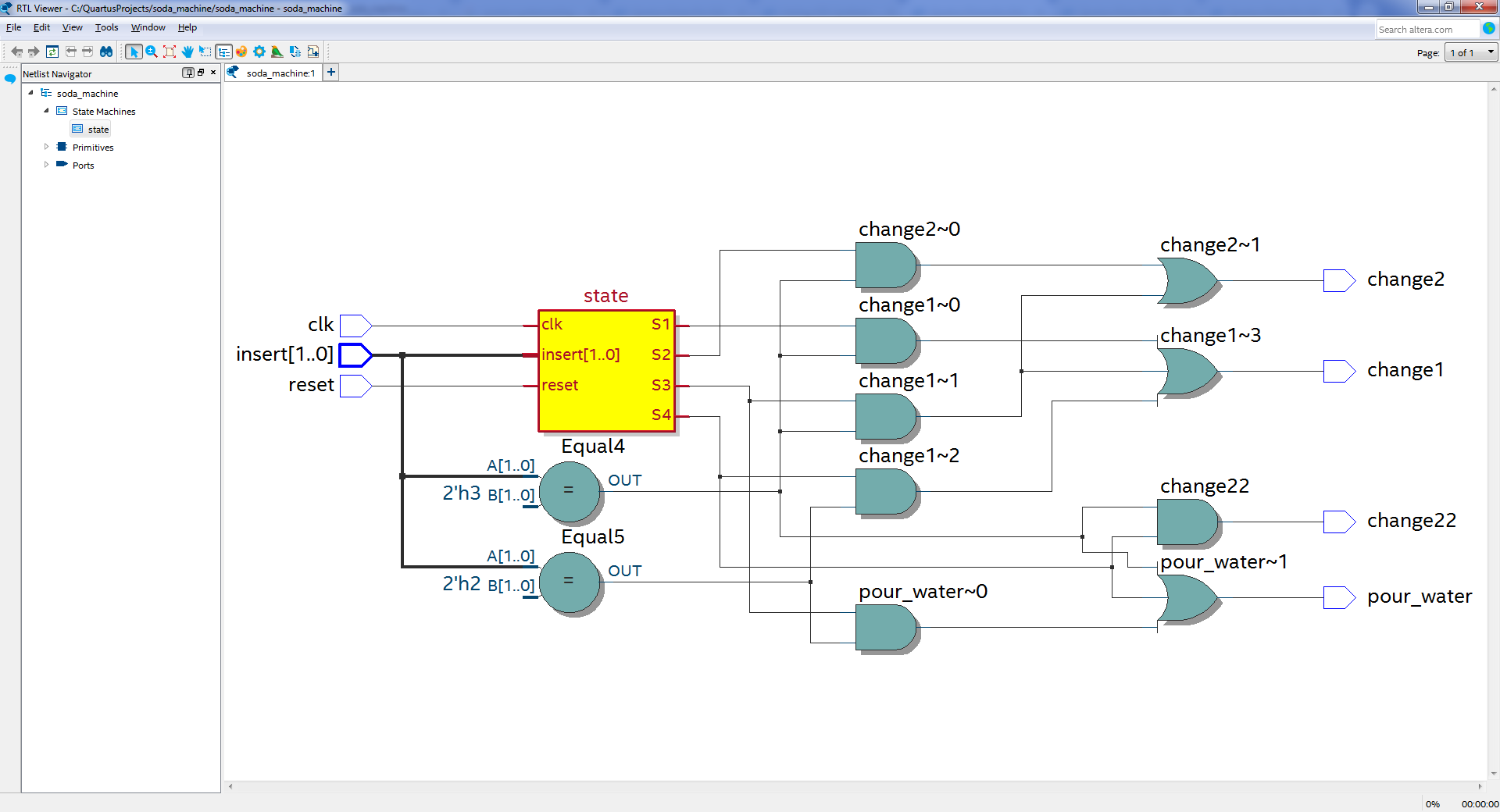

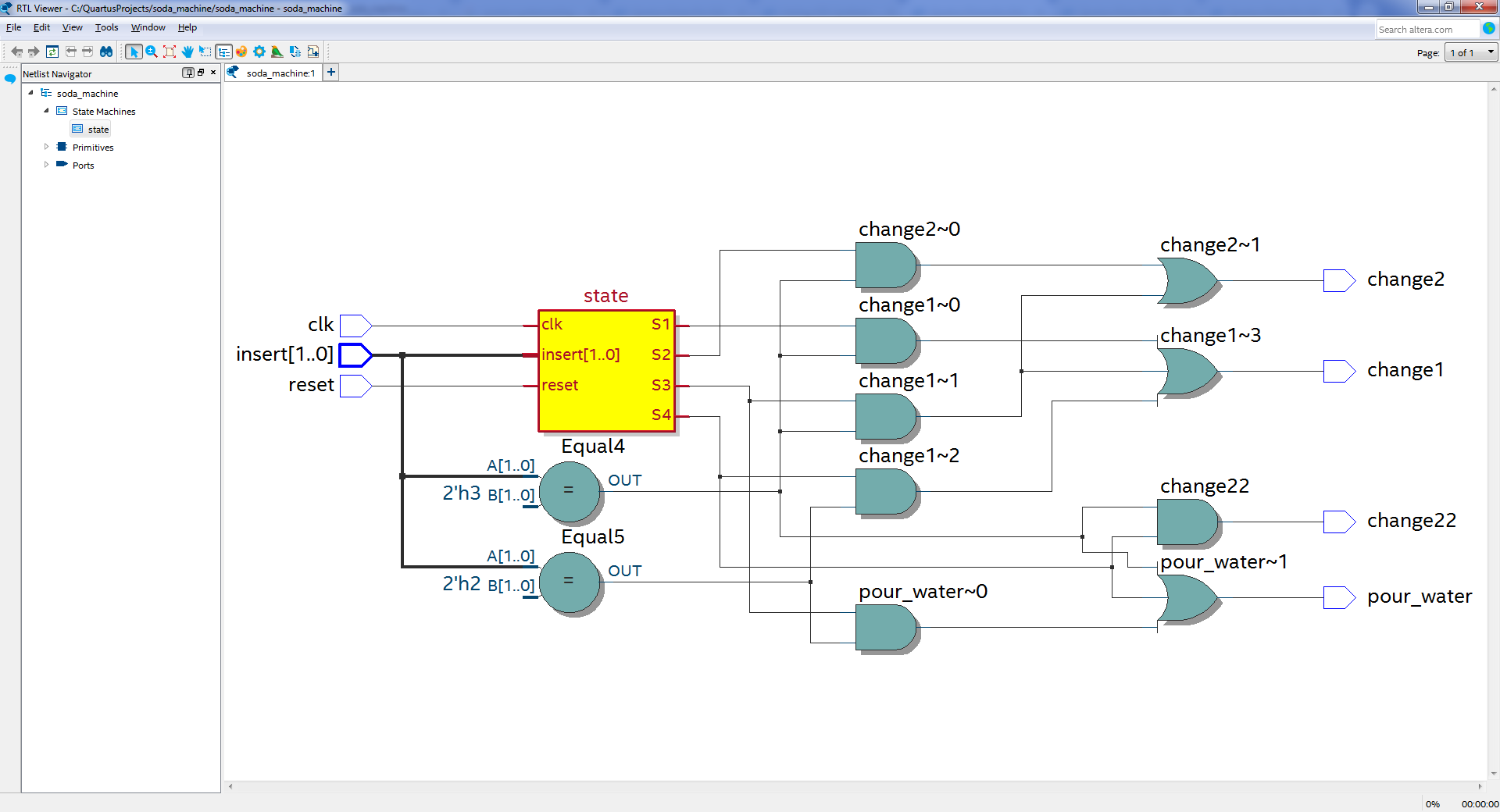

プロジェクトにファイルを追加するには、ファイル->新しい「SystemVerilog HDLファイル」を使用します。保存時に適切な名前を付けます。これらの2つのファイルを追加した後、処理->コンパイルの開始でプロジェクトをコンパイルできます。コンパイルが成功すると、結果のスキーマツール->ネットリストビューア-> RTLビューアが表示されます。

RTLビューア

ステートマシンの状態図を表示するにはツール->ネットリストビューア->ステートマシンビューア

ステートマシンビューア

Encodingタブで、Quartusが「ワンホット」エンコーディングスキームを適用したことがわかります。これは、各状態に個別のDトリガーが使用され、状態S 0が0ではなく0にエンコードされている場合です。これは、初期リセットスキームを簡略化するために行われます。状態。RTL Viewerが回路図を正確に表示するのではなく、概念を示していることに気付くでしょう。回路図を表示するには、ツール->ネットリストビューア->テクノロジマップビューア(フィッティング後)を使用します。

シミュレーション

原則として、現時点ではソーダ水を販売するマシンの回路がありますが、正しく機能することを確認する必要があります。このため、テストベンチを作成してsoda_machine_tb.svファイルに配置します。

soda_machine_tb.sv

`include "soda_machine_types.sv"

import soda_machine_types::*;

module soda_machine_tb;

insert_type insert;

logic [5:0] testvectors[10000:0];

int vectornum, errors;

logic clk, reset, pour_water, change1, change2, change22;

logic pour_water_expected, change1_expected, change2_expected, change22_expected;

//

soda_machine dut(

.clk(clk),

.reset(reset),

.insert(insert),

.pour_water(pour_water),

.change1(change1),

.change2(change2),

.change22(change22)

);

//

always

#5 clk = ~clk;

//

initial begin

//

$readmemb("../../soda_machine.tv", testvectors);

vectornum = 0;

errors = 0;

clk = 1;

//

reset = 1; #13; reset = 0;

end

//

always @(posedge clk) begin

#1; {insert, pour_water_expected, change1_expected, change2_expected, change22_expected} = testvectors[vectornum];

end

// ,

always @(negedge clk)

if (~reset) begin

if ((pour_water !== pour_water_expected) || (change1 !== change1_expected) || (change2 !== change2_expected) ||

(change22 !== change22_expected)) begin

$error("%3d test insert=%b\noutputs pour_water=%b (%b expected), change1=%b (%b expected), change2=%b (%b expected), change22=%b (%b expected)",

vectornum + 1, insert, pour_water, pour_water_expected, change1, change1_expected, change2, change2_expected, change22, change22_expected);

errors = errors + 1;

end

vectornum = vectornum + 1;

if (testvectors[vectornum] === 6'bx) begin

$display("Result: %3d tests completed with %3d errors", vectornum, errors);

$stop;

end

end

endmodule

モジュールをテストするには、テストベクターファイルsoda_machine.tvを使用します。

soda_machine.tv

01_0_0_0_0

01_0_0_0_0

01_0_0_0_0

01_0_0_0_0

01_1_0_0_0

10_0_0_0_0

10_0_0_0_0

10_1_1_0_0

11_1_0_0_0

10_0_0_0_0

10_0_0_0_0

11_1_0_0_1

10_0_0_0_0

11_1_0_1_0

01_0_0_0_0

01_0_0_0_0

01_0_0_0_0

11_1_1_1_0

最初の2ビットは挿入入力、次の4ビットは出力に対する期待です:pour_water、change1、change2、change22。たとえば、ファイルの先頭で、ルーブルコインが5回続けて挿入されます。5番目のコインでは、pour_water信号が表示されることを期待していますが、変更配送信号は非アクティブです。soda_machine.tvのファイルがされに追加ファイル- >新規「テキストファイル」プロジェクト。

のModelSimでの作業の都合上、追加soda_machine_run_simulation.doのファイルをして、以下の内容:

soda_machine_run_simulation.do

add wave /soda_machine_tb/dut/clk

add wave /soda_machine_tb/dut/reset

add wave /soda_machine_tb/dut/insert

add wave /soda_machine_tb/dut/state

add wave /soda_machine_tb/dut/nextstate

add wave /soda_machine_tb/dut/pour_water

add wave /soda_machine_tb/dut/change1

add wave /soda_machine_tb/dut/change2

add wave /soda_machine_tb/dut/change22

view structure

view signals

run -all

wave zoom full

シミュレーションを実行し、信号プロットをModelSimに出力します。soda_machine_run_simulation.doファイルがプロジェクトファイルに追加されます->新しい「Tclスクリプトファイル」

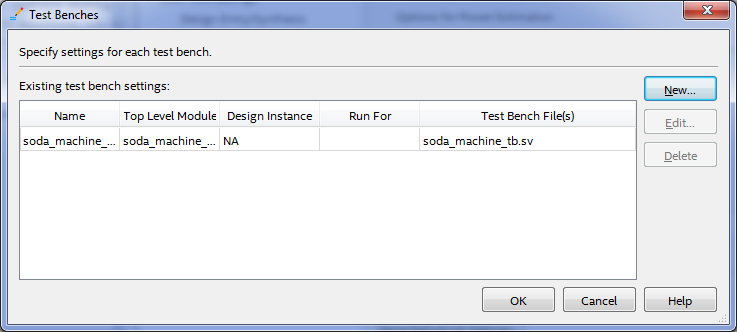

次に、シミュレーションが自動的に開始されるようにプロジェクトを設定します。メニュー項目[ 割り当て]-> [設定]を選択し、カテゴリ[EDAツール設定]-> [シミュレーション]を選択します。NativeLinkの設定、選択コンパイルテストベンチを:をクリックしてテストベンチのボタンを...でテストベンチのウィンドウが開き、クリックしてください新しいボタンを...で新しいテストベンチの設定、開いたウィンドウで塗りつぶしをテストベンチ名のフィールド:soda_machine_tbをウィンドウの下部にあるファイル選択ボタン...をクリックし、soda_machine_tb.svファイルを選択して、[ 追加 ]ボタンをクリックします。図のように表示されます。[新しいテストベンチ設定]

ウィンドウで、[ OK ]をクリックします。 [ テストベンチ]ウィンドウは次のよう になります。[ テストベンチ ] ウィンドウで、[ OK ]をクリックします。NativeLinkの設定、確認したシミュレーション設定するために使用するスクリプトをチェックボックスを選択しsoda_machine_run_simulation.doのファイルを。 [ 設定]ウィンドウ は次のようになり ます。[ 設定]ウィンドウで、

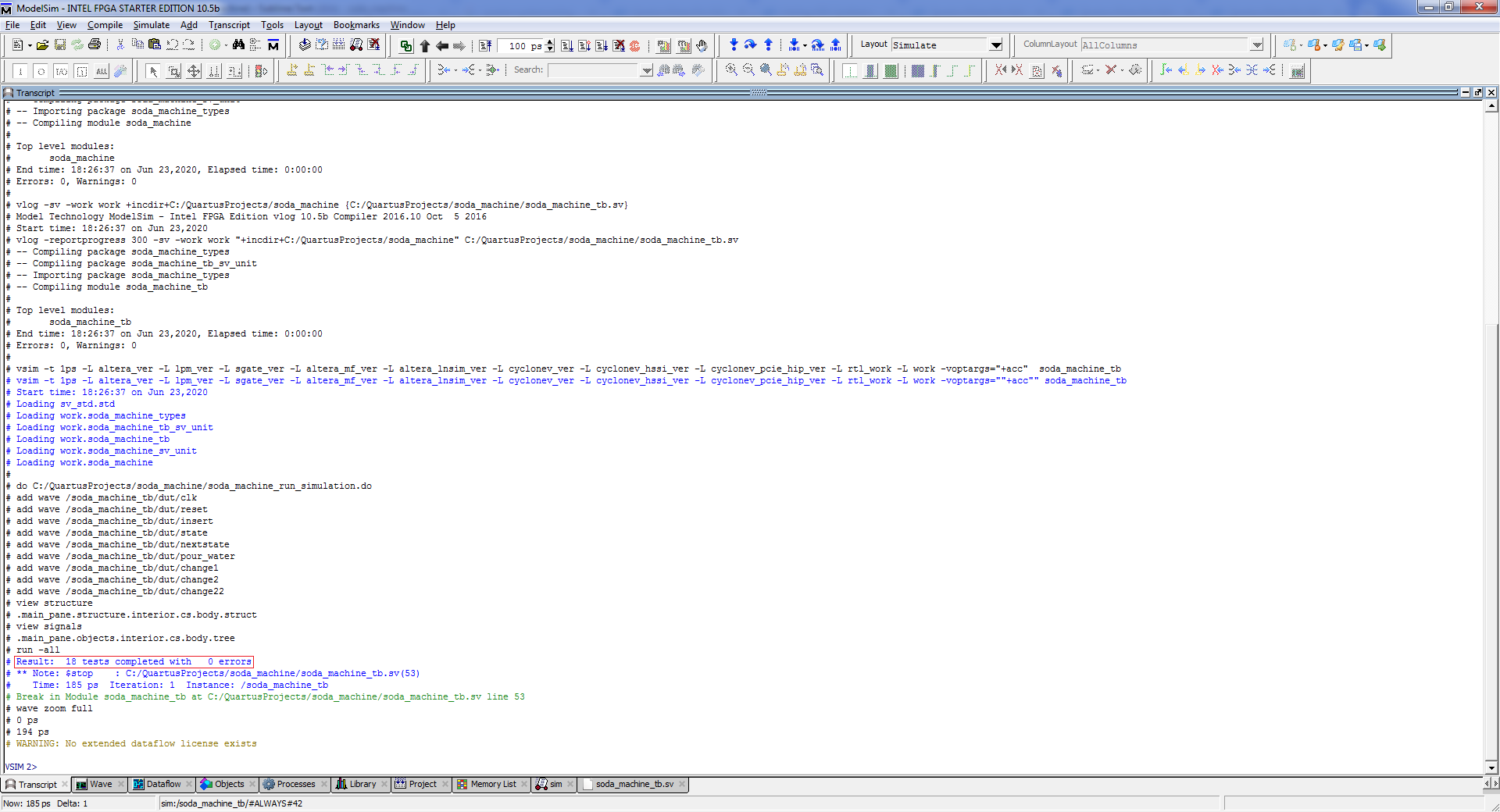

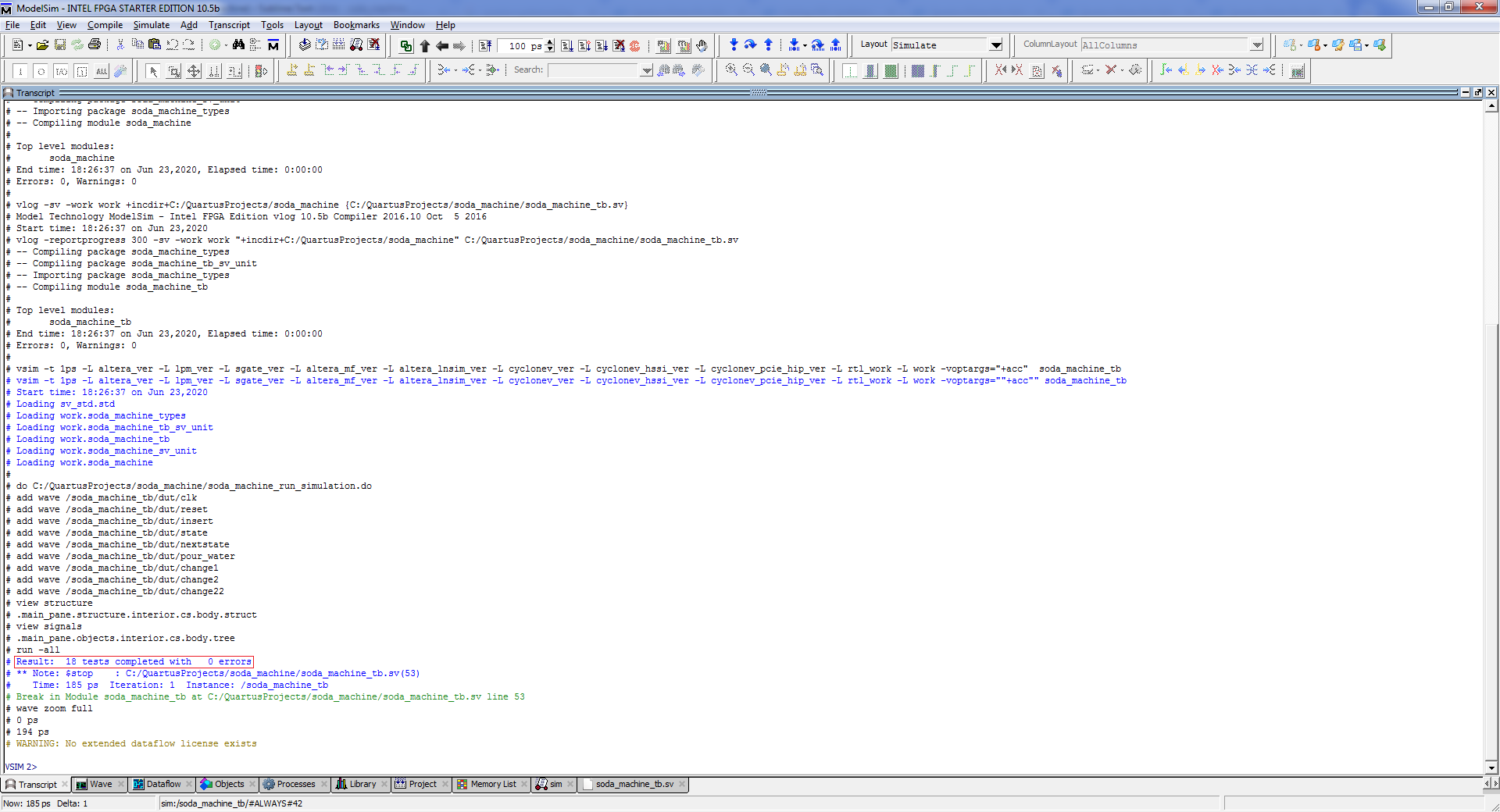

OK、我々はプロジェクトのコンパイル処理を- >スタートコンパイルは、我々はシミュレーション開始ツール] - > [ファイル名を指定して実行シミュレーションツール- > RTLシミュレーション。ModelSimがプロジェクトを起動してシミュレーションするはずです。文字起こしタブの外観:

ModelSimトランスクリプトタブ

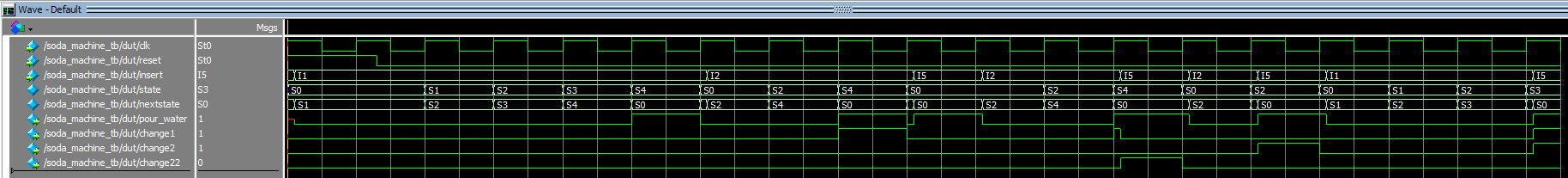

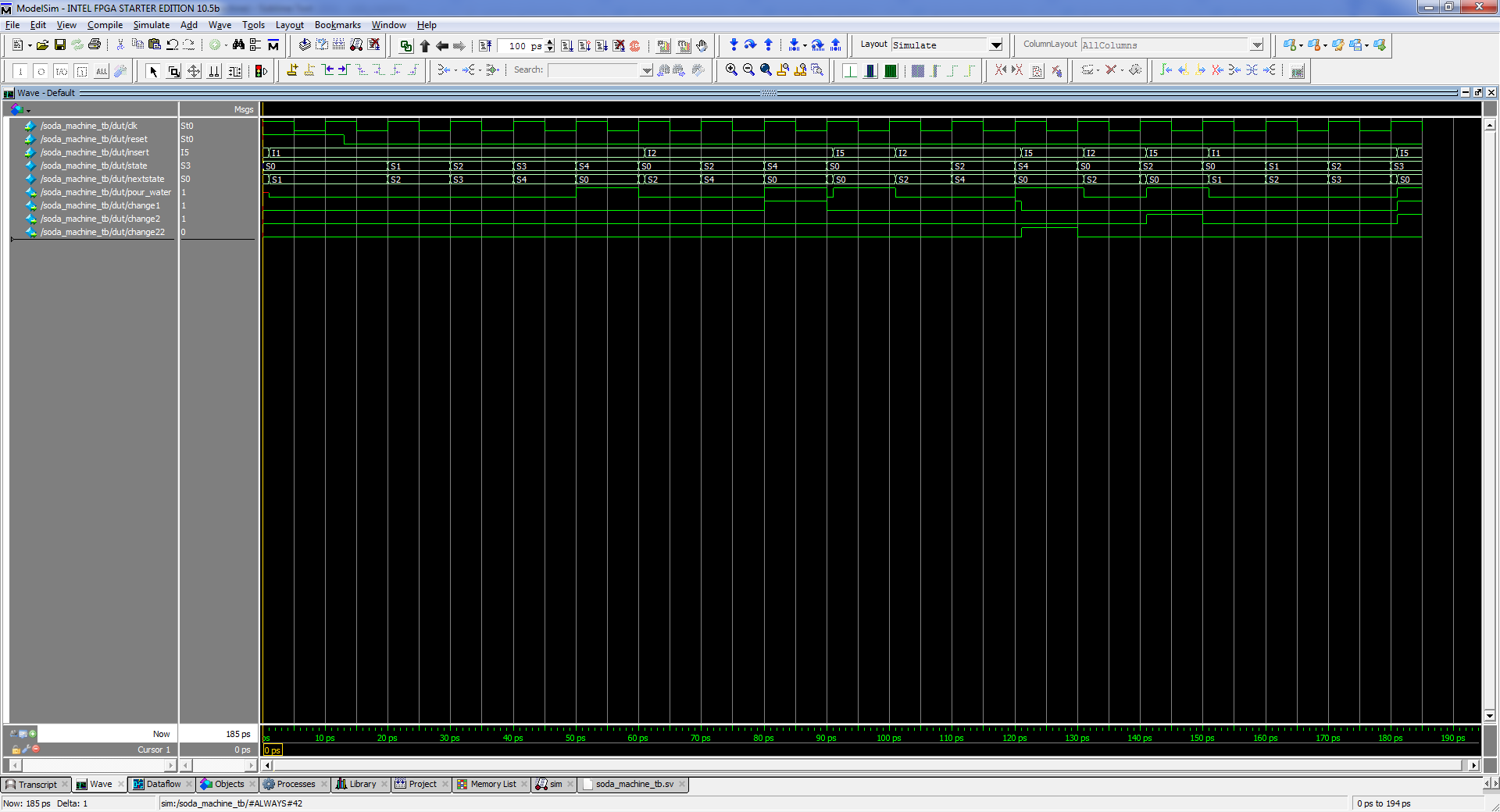

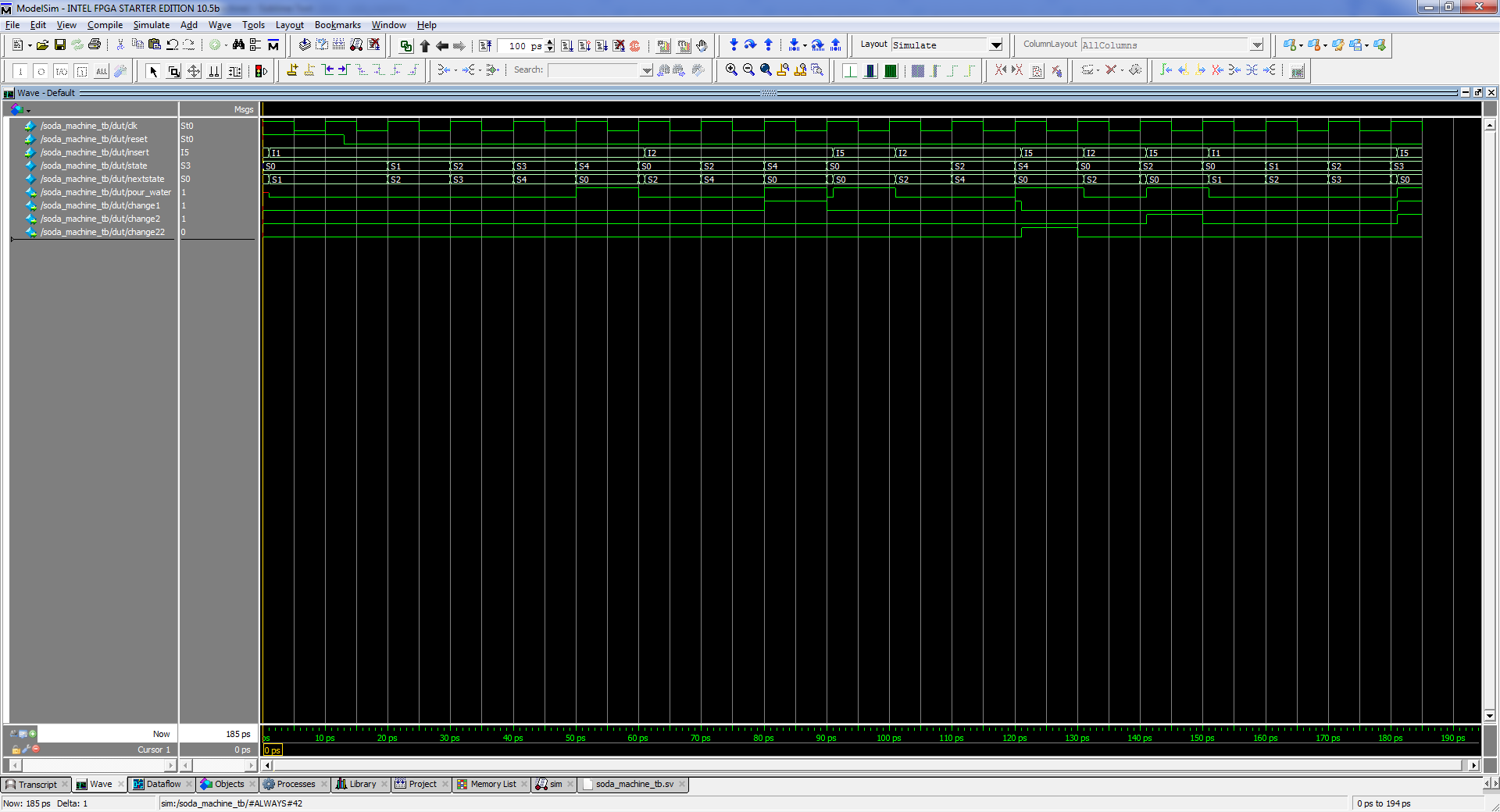

実行されたテストの数と検出されたエラーに関するテストベンチの出力は、赤で強調表示されています。[波]タブの外観:

ModelSim Waveタブ

プロジェクトのソースコード

プロジェクトのソースコードであるgithub.com/igoral5/soda_machineクローンプロジェクト、その後のQuartusのでプロジェクトを開くファイル- >プロジェクトを開く...

選択soda_machine.qpfファイルを。次に、プロジェクトをコンパイルします。処理->コンパイルの開始とシミュレーションツール->シミュレーションツールの実行-> RTLシミュレーションを開始します。