シリーズの以前の記事

通常のコンピュータプログラムはどのように機能しますか?特定の外部環境があります(「マウス」を備えたモニターとキーボードは、まさにこの環境の最も典型的な代表です)。プログラムはそれらと相互作用します。デバッグするときは、外部環境から実際の影響を与えることも、それらをエミュレートすることもできます。私たちのテスターは、外部の影響をエミュレートするだけのあらゆる種類のスクリプトを作成することがよくあります。その後、ログアナライザーが起動し、水曜日に回答が正しいことを確認します。

このコンピュータプログラムですべてにバグがある場合はどうなりますか?ブレークポイントを設定し、ブレークポイントがヒットした瞬間のシステムのスナップショットを調べることができます。システムスライスは変数の値です。たぶん、さまざまなミューテックスや他の同期オブジェクトの状態。一般に、デバッグされたシステムの内部パラメーターのスナップショット。

FPGAのデバッグ時には、同じことができます。確かに、環境が現実のものである場合、システムのセクションを停止して調査することは、可能ではありますが、問題があります。 Reddの話の一部として、私はすべてがシンプルで高速であるべきだという考えを推進し続けています。複雑なシステムは設計していません。前回の記事で行ったように、ある種のモジュールを実行しています。洗練されていますが、非常に単純です。一般的に、私たちはその行動モデリングを行います。

そしてここで、外部環境について疑問が生じます。それをシミュレートする方法は?モデルが私たちの助けになります。 Verilog(およびVHDLや他の同様のもの)は、あらゆるものの動作を記述することができます。 ULPIマイクロサーキットで動作するシステムを作成しています...したがって、その動作をテストするには、ULPIとまったく同じように動作する何かがもう一方の端にある必要があります。つまり、ULPIモデルです。しかし、これだけでは十分ではありません。私たちのブロックは、ALAVON_MMバスからのコマンドに反応します。ブロックをライブにするのはこのバスです。したがって、バスモデルAVALON_MMも追加する必要があり、このモデルはアクティブである必要があります。テストの影響を提出するのは彼女です。

最終的には、まさにそのようなシステムを作らなければなりません。そして、すべてのバス、さらにはモジュール内の信号のタイミング図を記録できるようになります。エラーが発生した場合、ブレークポイントを設定し、システムのスナップショットを調べて敵を見つけることができます。個人的には、通常これらのブレークポイントを設定しませんが、ほとんどの場合、タイミング図の分析で十分です。実際のところ、信号はインターフェイス信号だけでなく、内部の信号も表示できます。チャート上の12個または2個の内部信号を引き出すと、通常、ロジックで何が間違って実装されているかを推測できます。

今日の記事の目的は、モデリングが一般的に何であるかについて話すことではなく(これは長い話です)、このモデリングを最も迅速に行う方法を示すことです。そして、これを戦闘任務ではなく、簡単な例で検討します。非常に単純なテストシステムを作成して、次の記事で、より複雑なバージョンの脚がどこから成長するかをすでに理解できるようにします。これは、読んでいるときに座って不思議に思わない方が便利だからです。「なぜ彼はこれを行うのですか?」 ..。ちなみに、最近、私の知人の一人は、モデリングのスキルは持っていますが、Quartus環境にこれを簡単かつ自然に実行できるメカニズムが組み込まれていることを知りませんでした。彼はそれに必要以上の努力を費やした。したがって、おそらく誰かも、Quartusに固有の可能性について自分自身のために何か新しいことを学ぶでしょう。そう、始めましょう。

Verilog

人々は2つのカテゴリーに分類されます。手で一から作るのが好きな人、マウスで作るのが好きな人。手ですべてを作成する方が正しいです。あなたはすべての行動を制御し、あなたが知っているすべてを完全に行うことができます。しかし、メモリは信頼できません。彼女がいつも同じことをしている場合、彼女は詳細を念頭に置いており、常に言語を切り替える必要がある場合は、1〜2か月後にそこで何をする必要があるかを覚えておく必要があります。したがって、「マウスをいじくり回す」オプションを使用する作業は、これが理由である場合に限り、存在する権利があります。繰り返しになりますが、デバッグ中のモジュールに12個ほどのインターフェイス信号がある場合、それらを再宣言して転送するという日常的な作業を行うのはいつも退屈です。したがって、ここでは、マウスを使用してモデルを作成する方法を見ていきます。そして、これで十分かどうか、または手動作業に切り替える必要があるかどうかは、誰もが自分で判断します。

そこで、モジュールをシミュレートしたいと思います。 「シミュレート」とは、私たちのサイクルの範囲を超えています。このトピックについて、別の大きなサイクルを書くことができます。つまり、このセクションのフレームワーク内では、モデルを開発するための方法に精通していることを前提としています。しかし、すべてをプロジェクトに含める必要があります...またはそうではありませんか?奇妙なことに、モジュールをモデル化するために独自のプロジェクトを作成する必要はありません。新しいものを含めることなく、任意のプロジェクトに寄生虫として自分自身をアタッチできますが、メインアセンブリにまったく参加しないテストスイートを作成することによってのみ可能です。

興味を引くために、SystemVerilogのこのような面白いモジュールをULPIプロジェクトに添付しましょう。これは、特に説明のために私が作成したもので、開発されたアナライザーとは関係ありません。少し前に、チェックサムの計算をいじくり回していたので、頭に浮かびました。

module sum(

input clk,

input [7:0] data,

input we,

input sof,

output [15:0] sum

);

logic [15:0] temp;

always @ (posedge clk)

begin

if (we)

begin

if (sof)

temp <= data;

else

temp <= temp + data;

end

end

// -

//assign sum = (~temp)+1;

// :

assign sum = temp;

endmodule

データはバスを介して送られてくることがわかります。バスはAVALON_MMを非常にリモートで連想させ、単純に並列コードで出力されます。

結果のファイルをプロジェクトのディレクトリに配置しましょう。ただし、Quartusのプロジェクトには含めません。代わりに、そのために特別にテストスイートを作成します。これを行うには、メニュー項目[割り当て]-> [設定]を選択し、表示

されるツリーで、[EDAツール設定]-> [シミュレーション]の項目を探します。

ちなみに、緑色の枠で強調表示されているシミュレーションの種類について。おそらく誰かが最初の記事で、純粋に習慣からプロジェクトを作成するときにModelSim Alteraを選択すると言ったことを覚えていますか?遅かれ早かれ発砲しなければならなかったのは、まさにステージ上の銃でした。ただし、プロジェクトの作成時にモデリングタイプが選択されていなかった場合は、ここで選択または変更できます。

テストスイートの作成を続けます。ラジオボタンを[テストベンチのコンパイル]に切り替え(ちなみに、この用語はどのようにロシア語に美しく翻訳されますか?ベンチが表示されないため、「テストベンチ」を書くことはできません) 、[テストベンチ]ボタンを押します:

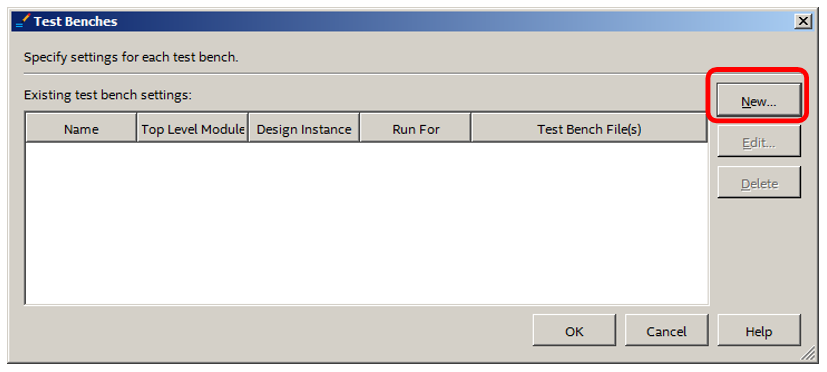

開いたダイアログで、[新規]を押します:

実行する場合テストケースを手動で、1回のパスでフィールドに入力できます。ただし、すべてをマウスで行うため、フィールドの一部のみを入力し、残りは後で入力します。テストベンチ名フィールドParazitという単語を入力しました(プロジェクトに寄生するだけのテストを他に何と呼ぶことができますか?)。その下にあるParazitという単語が自動的に入力されました。今は変更しませんが、将来的には変更する必要があります。また、「...」ボタンを使用して、デバッグする加算器のコードを含むsum.svファイルを選択し、「追加」ボタンを使用して、それをテストファイルのリストにプッシュしました。今のところ、それだけです。ダイアログを閉じる...

次に、ModelSim環境でテストを作成し続けます。これを行うには、[ツール]-> [シミュレーションツールの実行]-> [RTLシミュレーション]メニュー項目を選択します

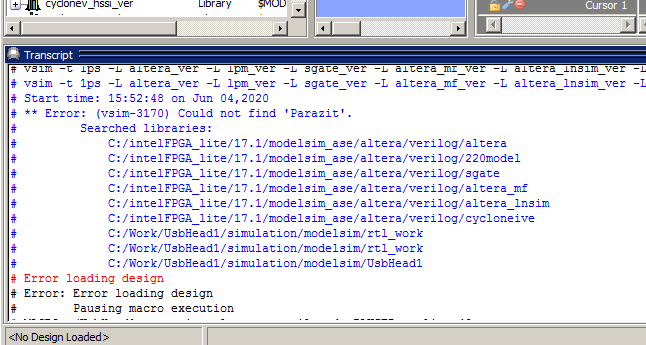

。ModelSimウィンドウが開きます。おそらくVerilogコードでエラーが見つかるので、ModelSimを閉じてエラーを修正し、再度開く必要があります。しかし遅かれ早かれ、間違いのリストは純粋に組織的なものになるでしょう。私には次のように見えます。

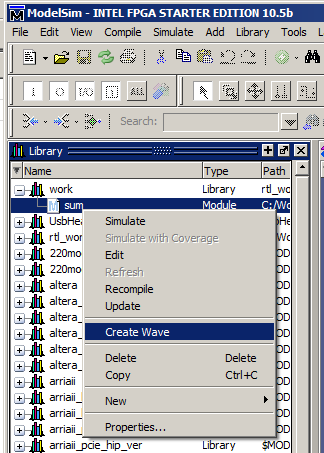

トップレベルのモジュールが見つかりません。これは正常です。まだ単純に作成していません。したがって、ライブラリのリストで作業して開きます。これが私たちの加算器です。

その上にカーソルを置き、マウスの右ボタンを押して、[ウェーブの作成]メニュー項目を選択します。これはすべてテキストで非常に退屈です。私がビデオを撮影している場合、プロセス全体に数十秒かかるので、心配しないでください。しかし、さらに手を見てください。したがって、Create Wave ...

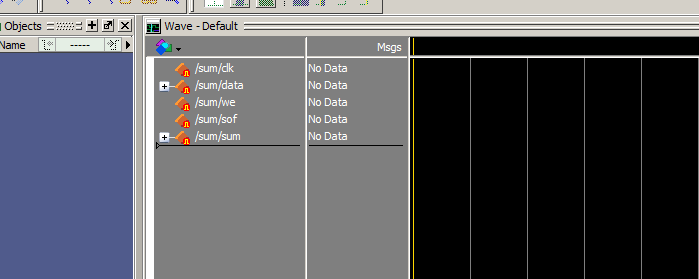

モジュールインターフェイス信号は自動的にチャートに移動しました。

それらの1つに値を割り当てる必要があります。どちらでも構いません。任命することが重要です。 Quartusの非常に古いモデリング環境は、クロック信号の生成に優れていました。残念ながら、ModelSimを取り付け始めたため、かなり前に配信から撤回されました。ここでは、そのようなものですべてがそれほど美しくはありません。ここではジェネレーターを生成する意味がわからなかったので、表示すらしません。だから...まあ、私たちの線をゼロに設定しましょう。信号を狙い、右ボタンを押して、メニュー項目[編集]-> [ウェーブエディター]-> [ウェーブフォームの作成/変更]を選択します。

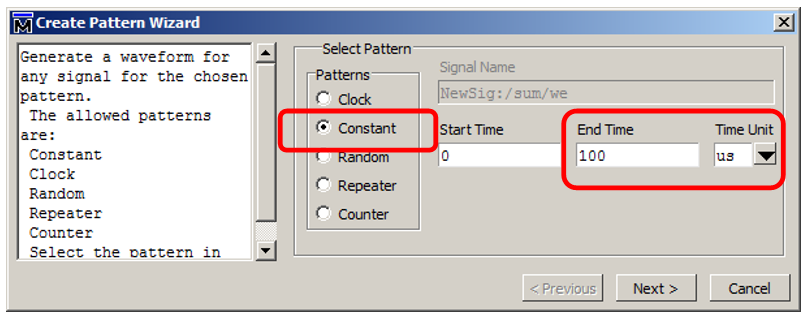

表示されるダイアログで、[定数]を選択します。同時に、たとえば100マイクロ秒ずつ時間を変更します。

次に、値0を示します。

最低限必要なデータセットを作成しました。残りはペンで簡単に実行できます。ファイルをエクスポートします。これを行うには、メニュー項目[ファイル]-> [エクスポート]-> [波形]を

選択します。ファイルタイプVerilogTestbenchを選択します(ちなみに、SystemVerilogではないのは残念ですが、将来的にはペンで修正できるようになります)。ファイル名も設定します。「どうして?」にちなんで、parazit_tbと名付けました。

それだけです。仮設住宅を保存する必要はありませんが、ModelSimを閉じることができます。

次にモデルをどうするか

これはそのような曲がった、しかしまだ既製のVerilogファイルであり、システムは私たちのために作成されました:

`timescale 1ns / 1ns

module parazit_tb ;

reg sof ;

reg we ;

wire [15:0] sum ;

reg [7:0] data ;

reg clk ;

sum

DUT (

.sof (sof ) ,

.we (we ) ,

.sum (sum ) ,

.data (data ) ,

.clk (clk ) );

// "Constant Pattern"

// Start Time = 0 ns, End Time = 100 us, Period = 0 ns

initial

begin

end

initial

#0 $stop;

endmodule

自動化により、ビルディングブロックを作成する必要がなくなりました。さらに、より多くのインターフェース信号があれば、自動化はすべての回路を素直に登録して接続します。個人的に、私が手動でテストスイートを作成するとき、気のめいるのは信号とその転送を記述するプロセスです。ここで、このファイルに、デバッグされた合計モジュールに影響を与える環境モデルを作成します。

ご覧のとおり、オシレーターの定数を設定しても意味がありません。しかし、それでも、すべての回路が作成され、テスト対象のモジュールが接続され、最初のセクションも作成されています。コードを改良してみましょう。 1つ目は、行を削除してブレークポイントを削除することです。

initial

#0 $stop;

次に、クロックジェネレーターモデルを追加します(古いQuartusesによって作成された素晴らしいジェネレーターが恋しいです!そこで周波数をメガヘルツで設定し、周期で再計算することを考えないでください、さらには半周期です)。

always

begin

clk = 0;

#5;

clk = 1;

#5;

end

次に、いくつかのデータバイトを送信する必要があります。これを行う最も簡単な方法は最初のセクションにありますが、そこに各バスアクセスフェーズを記述すると、このセクションのコードは混乱します。したがって、私は次のタスクを実行します(タイヤモデルとして機能するのは彼女です)。

task SendByte (input reg[7:0] D);

begin

data = D;

we = 1;

@(posedge clk);

#1

we = 0;

end

endtask

さて、最初のブロックでバスを操作するための定数の目的とサイクルの呼び出しを記述します。レコードタイプ#123は「123単位の時間待機」を意味することを思い出させてください。ナノ秒でそれを持っています。また、割り当てはシーケンシャルであるため、「矢印」ではなく「等しい」操作を使用することを思い出してください。したがって、次の主要なテストコードがあります。

ここを見る

initial

begin

sof = 0;

we = 0;

data = 0;

#13;

//

sof = 1;

SendByte (1);

//

sof = 0;

SendByte (5);

SendByte (1);

//

#20;

SendByte (1);

end

全体として、完全なモジュールコードは次のようになります。

完全なモジュールコードを表示します。

`timescale 1ns / 1ns

module parazit_tb ;

reg sof ;

reg we ;

wire [15:0] sum ;

reg [7:0] data ;

reg clk ;

sum

DUT (

.sof (sof ) ,

.we (we ) ,

.sum (sum ) ,

.data (data ) ,

.clk (clk ) );

always

begin

clk = 0;

#5;

clk = 1;

#5;

end

task SendByte (input reg[7:0] D);

begin

data = D;

we = 1;

@(posedge clk);

#1

we = 0;

end

endtask

// "Constant Pattern"

// Start Time = 0 ns, End Time = 100 us, Period = 0 ns

initial

begin

sof = 0;

we = 0;

data = 0;

#13;

//

sof = 1;

SendByte (1);

//

sof = 0;

SendByte (5);

SendByte (1);

//

#20;

SendByte (1);

end

endmodule

テストケースの準備を完了する

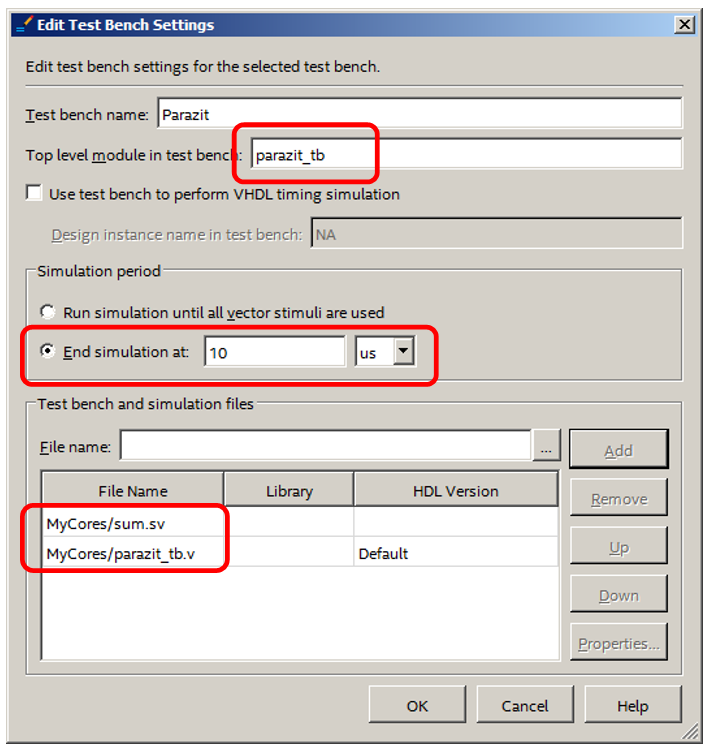

このテキストをテストスイートに追加するときが来ました。これを行うには、すでに認識されているダイアログに移動し

ますが、ここではセットを作成せず、リストから選択します。将来的には、セットが追加されるにつれてリストが大きくなります...選択したら、[編集]ボタンを押します。設定を3回編集しました。

- parazit_tb.vファイルをリストに追加しました。

- parazit_tb.vファイルでは、トップレベルモジュールの名前はparazit_tbであるため(前のセクションのソースを確認することで確認できます)、テストベンチ行のトップレベルモジュールにこの名前を入力しました。

- シミュレーションを10マイクロ秒実行してから一時停止すると言いました。どちらかといえば、手動制御ボタンを押して行います。

合計

すべてを閉じます。ModelSimを再度実行します。すべてが正しく機能していることがわかります。データが入り、金額にカウントされます。クロック(上のデータがない場合、我々はゼロである)、量は増加しません。

モデリング環境自体の使用方法は、いくつかの記事のトピックです。むしろビデオ形式で。しかし、一般的に、Quartus環境からVerilog言語でテストをすばやく準備して実行する方法に精通しました。

シミュレーションをすばやく実行する方法がわかったので、USBアナライザーヘッドの環境モデルをスケッチして、その動作をテストできます。同時に、Quartusでは「マウス」を使用してすべてを構成できるため、ModelSimのスペルは1つも記憶していません。彼は必要なすべてのスクリプトを自分で生成し、ModelSim環境を自分で呼び出します。また、モデルのベースを自動モードで作成しましたが、手動で変更する必要がありました。

ああ、ああ。外部環境の要素の1つは、ULPIモジュールです。自分でモデルを開発するには、まず、そのマイクロ回路の動作のロジックを注意深く理解する必要があります。そして前回の記事で私はそれが非常にトリッキーだと言いました。第二に、モデルコードの開発に多くの時間を費やす必要があります。そして、その中のエラーの排除...既製のものを見つける方が簡単であることは明らかです。しかし、既製のモデルはSystemC言語でのみ見つかりました。したがって、次の記事では、この言語を使用してシステムをモデル化する方法を学習します。