宇宙船の電子機器を設計する仕事を得る方法を知りたいですか?最近、Blue OriginのFPGAデザイナーのポジションについてインタビューの申し出を受けました(上記を参照)。個人的にはそのようなポジションは必要ありませんが(すでに他社でASICデザイナーのポジションを持っています)、Blue Originの応募者の技術的要件は、9月15〜17日に開催される学童および中学生向けのセミナーの内容と完全に一致していることに注意しました。RUSNANOの支援を受けて、Skolkovoで開催されたChipEXPO展示会で。もちろん、セミナーでは、VerilogとFPGAテクノロジーについて、基本的な概念と単純ですがすでに興味深い例という非常に初期のレベルでのみ触れます。その後BlueOriginで仕事を得るには、まだ数年の研究と仕事が必要です。

コロナウイルスのため、セミナーは遠隔地で行われるため、モスクワの学童や学生だけでなく、ロシア、ウクライナ、カザフスタン、カリフォルニア、その他の国や地域のすべてが参加できます。 MIET、HSE MIEM、MIPT、Chernihiv Polytechnic University、Samara University、IVA Technologies、およびfpga-systems.ruの講師とエンジニアが、物理的に講義を行い、参加者をリモートで支援します。

最初に参加するには、セミナーの前であっても、「スマートナノチップの作成者のしくみ」という一般的なタイトルで、RUSNANOの理論コースの3つの部分、「トランジスタからマイクロ回路へ」、「デジタル回路の論理的側面」、「デジタル回路の物理的側面」を完了する必要があります。このコースは、ワークショップ中に何をしているかを理解するために不可欠です。理論的なオンラインコースの修了証明書を受け取ると、モスクワのRUSNANOオフィスに行き、実践的なセミナーの無料料金を受け取ることができます(滞在する場合は、学童が優先されます)。このボードを使用すると、Skolkovoセミナーの前、最中、後に自宅で作業できます。

支払いの方法、セミナーの準備、およびその内容:

支払いを受け取る方法の説明は、STEMfordサイトにあります。 STEMfordはから小学生のための教育プログラムであるeNano、インフラ教育プログラムのためのRUSNANO財団の子会社。訪問するオフィスは次のとおり

です。ラボの前に、コンピューターにIntel Quartus Prime LiteEditionをインストールする必要があります。これを行う方法の説明は、A。Yu。Romanov、Yu。V。Panchulが編集した本「DigitalSynthesis:APracticalCourse」の無料の断片にあります。 DMK Press、2020

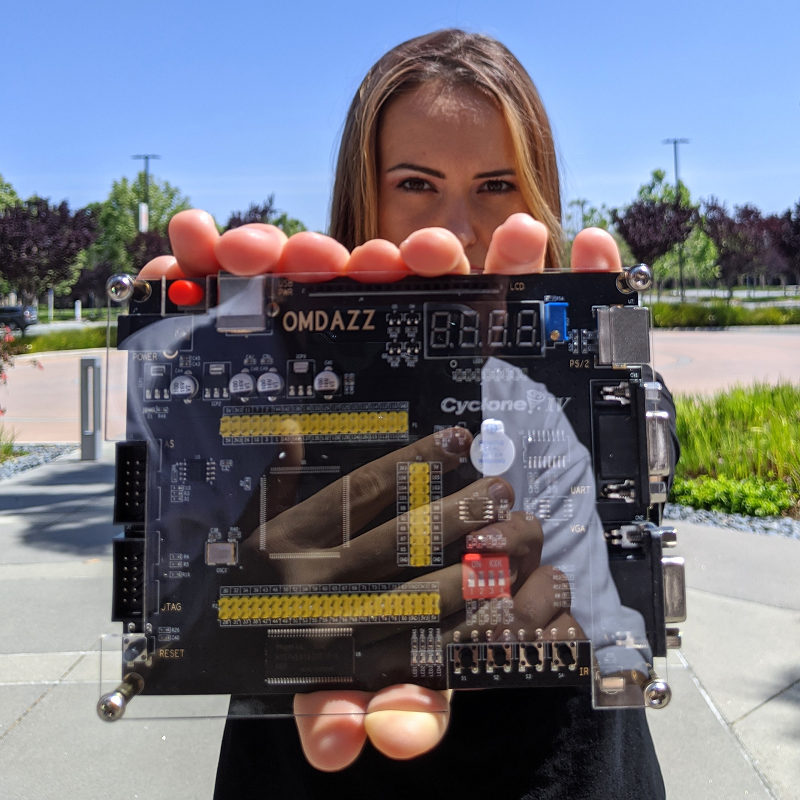

年。一般に、「Digital Synthesis」はセミナーに役立つ本であり、たとえば、schoolMIPS教育プロセッサの代わりに、より現代的なものですが、セミナーでいくつかのバリエーションで提示される演習について説明しています。schoolRISCV:Digital Synthesisの 本の最後に、新婚のVladislavとElena Sharshinのカップルとのかなり面白いインタビューがあります。彼らは、同僚のAndrei Papushinと一緒に、InnovateFPGAコンペティションで銀メダルを獲得するためにカリフォルニアに持ち込み ました。セミナーで使用されるボードの1つです。場合はあなたのために十分なボードが存在しないか、またはあなたが学生でない場合、あなたは他の場所AliExpressのとオンボードの注文することができます:1、2、3、4: セミナーで何が起こるのだろうか?プログラムの一部は次のとおりです。

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

1日目は、ハブレに関する記事に記載されている昨年のモスクワでのセミナーの開催経験に基づいています。

2日目は、昨年のゼレノグラードでのサマースクールとサマラでのセミナーの開催経験に基づいています。

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

3日目は、StanislavZhelnioとAlexanderRomanovのプロセッサーに関する教育プログラムの経験に基づいています。彼らがschoolMIPS学習プロセッサを開発して使用する前にのみ、そして今はschoolRISCVを使用します。 RISC-Vアーキテクチャは、MIPSおよび他のRISCアーキテクチャ(SPARC、ARM、POWERなど)と非常に似ていますが、単純なプロセッサでは意味がありますが、複雑なプロセッサ(SPARCのレジスタウィンドウ。大きなスタック。Rev6までのMIPSの分岐遅延スロット。これは、命令を順次フェッチする単純な静的パイプラインには適していますが、動的パイプラインなどでは問題になります)。

ロシアにはRISC-Vアーキテクチャでプロセッサを設計している企業が少なくとも3社あり、これは将来のハイエンドのロシアの組み込みプロセッサ、場合によってはデスクトップおよびサーバープロセッサの候補として適しています。また、RISC-Vは自信を持ってMIPSに取って代わります。世界の大学での建築的および微細構造的実験のための馬は、それについて学童に教える方が良いです。

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

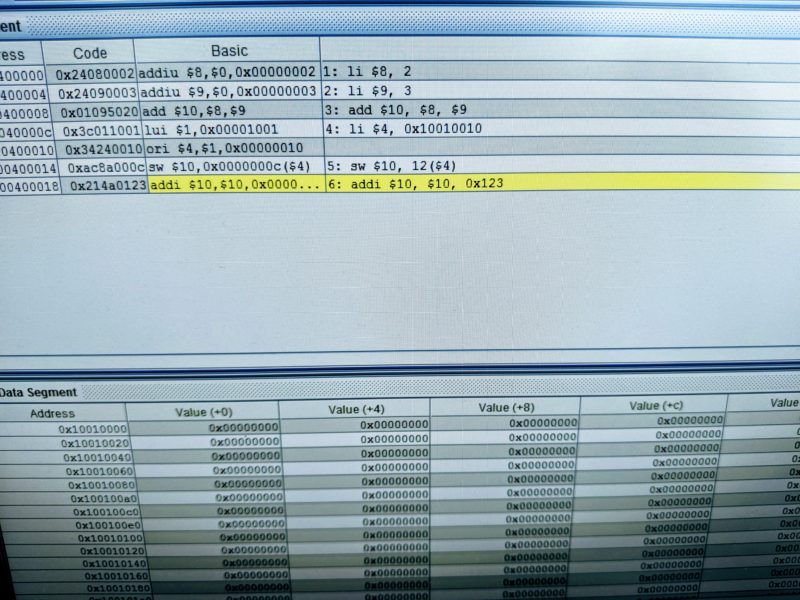

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00。結びの講義:デジタル回路設計を習得し、この知識を組み込みシステムと人工知能コンピューティングアクセラレータの設計に適用するための次のステップ。

アレクサンダーユリエビッチロマノフ。

18.00-21.00。学生がプロセッサを変更し、それを周辺機器と統合するための追加の演習と個々のプロジェクト。参加大学のマイクロエレクトロニクスの学部生と大学院生の助けを借りて。

去年の夏、ゼレノグラードで学童に教えているスタニスラフ・

ゼルニオです。スコルコボの仮想ChipEXPOでのセミナーでお会いしましょう!MIET、HSE MIEM、MIPTの先生方の協力を得て、イベントの一部を開催してライブを行いますが、ウイルスが許せない場合は分散して実施します。