ただし、DAC / ADCの使用またはデバッグは、使用するソフトウェアやデバイスの制御方法など、ハードウェアの製造元によって設定された制限のために困難な場合があります。これは、独自の相互作用モデルを設計することを示唆しています。

この記事では、FPGAを使用してPCとDAC / ADC間の相互作用を整理する可能性について検討します。

序文

この記事の主な目的は、特定の問題の解決策と、集積回路(IC)の相互作用のインターフェースについての知識を説明することです。DAC / ADCの主な目的はここでは考慮されていません。

この記事では、オブジェクト指向のプログラミングと回路に関する知識が必要です。したがって、これらの概念に精通していない場合は、それらから始めることをお勧めします。

電子機器の通信の問題に最初に遭遇した人の経験が誰かに役立つことを願っています。

皆さんの幸運と新しい成果!

インターフェイスに関する小さな教育プログラム

免責事項

IC通信に使用される主要なインターフェースの構造に精通している場合は、この点をスキップしても問題ありません。

教育プログラム

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

, . . . , .

, . , , .

(-/)

:

. .

, .

: , «» .

. .

:

. . . ( – , – , , ). « » ( ). .

, , .

() SPI I2C UART.

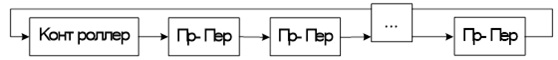

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

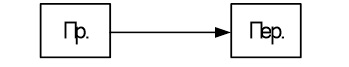

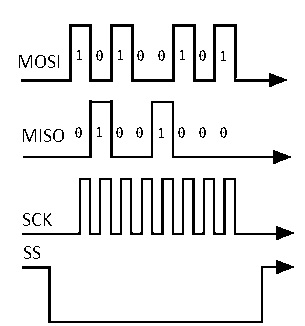

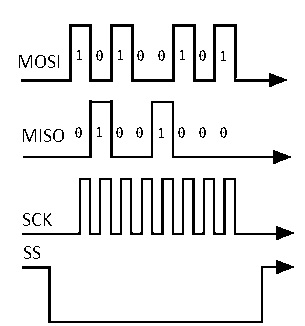

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

, .

, (, .) . , .

, . , , , .. , . . – , . , . , .

, .

( ), :

- «-»;

- «»;

- «» («»).

«-» — , . , — .

«» (, « » «») , . . , , , . .

( «») . , , , - . .

:

- ;

- ;

- -.

, . . . , .

, . , , .

(-/)

:

- ();

- ();

- ().

. .

, .

: , «» .

. .

:

- ;

- .

. . . ( – , – , , ). « » ( ). .

, , .

?

() SPI I2C UART.

I2C

I2C – . I2C . I2C «-», .

, , . , . 7- 16 . , 112 . I2C (SDA) (SCL).

I2C

SPI

SPI – , .

SPI «-». MOSI SCLK, . MISO, . SS.

SPI

UART

UART – – , .

RxD ( ) TxD ( ).

UART TxD . . UART , , UART , . , . 8 ( ), , .

UART «-». , UART . « » «».

UART

このDACは何ですか?

これではないようです

まず、使用するDAC / ADCを定義しましょう。

アナログデバイスAD9993-EBZデバッグボードは、4つの14ビットADCと2つの14ビットDACを組み合わせたデバイスです。

このICの動作モードは、内部レジスタの状態を変更することによって制御されます。 AD9993は、格納された(処理された)ワードサイズが8ビットの66個のレジスタを使用し、そのアドレスは3ビットの16進値(12データビット)で記述されます。読み取りコマンドと書き込みコマンドの2種類のコマンドがサポートされています。つまり、ICの動作を修正するためには、特定のレジスタアドレスに有効な8ビット値を書き込むコマンドを送信する必要があります。このICのレジスタへのアクセスは、シリアルペリフェラルインターフェイス(SPI)を介して実行されます。この接続は、40ピンFIFO_0コネクタまたは追加で取り付けられたコンタクトグループを介してデバッグボード上で実現されます。

このように(FIFO_0-上部の灰色のコネクタ)

SPI制限パラメーターの基本要件:

- 最大データ送信周波数-25MHz;

- 同期信号生成ラインの上位レベルと下位レベルの期間は10nsです。

- データ伝送ラインおよび解像度ラインでのレベル設定時間-2ns;

- データ伝送ラインおよび解像度ラインでのレベル保持時間-2ns;

- スレーブデバイスの伝送ライン上の1つのデータビットの有効性の保証時間は2nsです。

デバイスの機能の完全な説明は、そのドキュメントに記載されています。

メーカーは何と言っていますか?

推奨される制御方式

AD9993-EBZのドキュメントに基づいて、ICを制御するための推奨される方法は、40ピンポートを介してICに接続され、USBインターフェイスを介してPCに接続されたAnalog DevicesHSC-ADC-EVALCデバッグボードを使用することです。

SPIControllerは制御ソフトウェアとして使用されます。

推奨される

アナログデバイスHSC-ADC-EVALC回路(ザイリンクスVirtex-4 FPGAベース)

短所:

- 高価。AnalogDevicesの公式ウェブサイトにあるデバッグボードHSC-ADC-EVALCは698.28ドルで提供されています。

- 不便なユーザーインターフェース。SPIControllerソフトウェアは、レジスターの書き込みと読み取りの主な機能に加えて、コマンドの保存または開始のスケジュールを設定する機能を提供しません。

- . SPI SPIController, . Analog Devices, SPI.

SPIController

:

- .

HSC-ADC-EVALC

アナログデバイスHSC-ADC-EVALCボードをDAC / ADC制御デバイスとして使用することはその主な目的ではないことに注意してください。

HSC-ADC-EVALCは、主にADCのバッファメモリカードとして使用されますが、接続されたカードがサポートしている場合は、SPIを介してデバッグカードを構成する機能もあります。

独自の相互作用モデル

中間装置を使用する理由

AD9993-EBZがプログラムされているSPIは、最新のPCの一般的なインターフェイスではないため、DAC / ADCとPC間の相互作用を直接編成できないことは明らかです。

この問題を解決するには、コンピューターから送信されたUSBインターフェースからICがサポートするSPIインターフェース形式にデータを変換する中間デバイスを使用する必要がありました。

オプションを検討する過程で、Cyclone VFPGAに基づくTerasicDE10-Nanoデバッグボードを使用することになりました。

独自の相互作用モデル

なぜFPGAはとてもクールなのですか?

FPGAを使用する主な利点:

- . DE10-Nano , , , . IDE, Verilog.

- . DE10-Nano HSC-ADC-EVALC ($110 $698.28). DE10-Nano , .

- . , .

- . FPGA- (FPGA – field-programmable gate array – , ), ( ). rocketboards c .

...

相互作用モデルの設計中に、GPIO(汎用ピン)に基づくSPIインターフェースを実装することが決定されました。その接点ベースは、DE10-Nanoで使用できます。FPGAベースのSPIコントローラーの実装では、同様のトピックに関する資料が大量にあるため、特別な問題が発生することはありませんでした。

ただし、USBインターフェイスを介してFPGAをコンピューターに接続する実装では問題が発生しました。

DE10-Nanoには次のUSBポートがあります。

- FT232Rチップを搭載したUSBmini-Bで、UARTからUSBへの接続を実現。

- USBインターフェイスの物理層を実装するSMSCUSB3300チップによって制御されるUSBmini-Bは、FPGAのプログラミングにも使用されます。

これらのポートの使用は、DE10-NanoがいわゆるHPS(ハードプロセッサシステム)を介してこれらのポートと通信するという事実によって複雑になります。これは、マイクロプロセッサモジュール、ARM Cortexプロセッサ、フラッシュメモリコントローラなどを含むCyloneVチップの一部です。 HPSとFPGAの主な違いは、HPSは不変の構造のブロックであり、特定の機能用に最適化されており、プログラミングツールがない(したがって難しい)ことです。

Cyclone VチップのHPSおよびFPGAパーツには、独自のピンがあります。これらのピンは、HPSとFPGAの間で自由に共有されません。 HPS連絡先は、HPSで実行されているソフトウェアによって構成されます。 FPGAピンは、HPSまたはその他のサポートされている外部ソースを介してFPGA構成イメージを使用してプログラムされます。

Cyclone Vチップのプログラム可能なロジックとこれらのポートとの相互作用を整理するには、HPSで実行される特別なLinuxブートローダーを作成する必要があります。また、使用可能なUSBポートのコントローラーからFPGAの空き接点に信号を送信できるプログラムを開発する必要があります。

知識の現段階では、この質問は圧倒的であることが判明したので、別の方法を見つけることにしました。ただし、同様の問題に直面し、それを理解することにした人にとっては、考えられる解決策についての記事を読むと役立つ場合があります。

出口があります!

インターネットを徹底的に調べた結果、外部UARTコントローラーを使用することにしました。

外部UARTコントローラーは、FT232RLチップをベースにした小さなボードです。ボードには、コンピューターと通信するためのminiUSB-Bコネクターと、マイクロコンピューターおよびデバイスと通信するための6ピンコネクターがあります。

コントローラは、USBインターフェイスを介してPCに接続され、GPIOコンタクトベースを介してDE10-Nanoに接続されます。

Waveshareのコントローラー自体(プロジェクトで使用)

USB経由でUARTインターフェイスを使用してPCからデータを転送すると、複雑で多層のUSBプロトコルデバイスを処理する必要が実質的になくなります。これ以降、このタスクはシステムにプリインストールされているか、ユーザーが個別にインストールしたドライバーに割り当てられるため、USBインターフェイスを介した対話は問題ではなくなります。

電力線と接地線、およびデータ送信線と受信線に加えて、RTSおよびCTSとして署名されたピンがボード上にあります。これらの接点は、いわゆるフロー制御に使用されます。これは、回線の状態に応じて、マスターデバイスまたはスレーブデバイスからデータを受信する準備ができていることを通知するように設計されたメカニズムです。これらの行を使用する必要はないため、メカニズムを無効にするには、コンピュータードライバーの設定で、フロー制御が使用されていないことを示す必要があります(これは通常デフォルトの構成です)。

Windows PCに接続すると、UARTコントローラーは仮想シリアルポートとして検出されます。したがって、PCと対話するためのスキームの開発は、シリアル仮想ポートと対話する機能を備えたソフトウェアの作成、およびUARTインターフェイスを介したデータの送受信を実装するFPGAのプロジェクトの開発に帰着します。

外部UARTコントローラーは、実際にはすでにDE10-Nanoにあるコントローラーの完全なアナログですが、その唯一の利点は、FPGAの空きピンに直接接続できることです。このようなデバイスのコストは5ドルから10ドルの範囲です。

ソフトウェア開発

一般情報

すでに述べたように、PCのソフトウェア開発は、仮想シリアルポートとの情報交換をサポートするプログラムの作成に限定されます。ソフトウェア開発に利用可能なソフトウェアツールの分析中に、RTXTライブラリを使用するJava第8版のプログラミング言語が選択されました。

Javaは、多くの重要な機能を備えた、厳密に型指定されたオブジェクト指向のプログラミング言語です。特に、Javaプログラミング言語で記述されたプログラムは、特別なバイトコードに変換されます。これにより、Java仮想マシンが実装されている任意のコンピューターアーキテクチャで実行できます。

Java標準ライブラリには、仮想シリアルポートと対話する機能がありません。これは、RTXTライブラリが使用された目的です。 RTXTは、無料のソフトウェアライセンスの下で配布されます。ライブラリは、インターフェイスと対話するシステム実装を使用し、シリアルポートを使用した解析、接続、読み取り、および書き込み操作のためのクラスを提供します。このライブラリの詳細については、こちらをご覧ください。

古いが信頼性の高い組み込みのSwingライブラリは、ユーザーインターフェイスを開発するためのツールとして使用されます。変更のテーマに能力のためには、スイング中にシンプルなUIは見えないかもしれない

プログラム自体は非常にシンプルで、主にRTXTライブラリの文書化された機能を使用します。

プログラムの主な機能

使用可能なポートは次のように決定されます。

public String[] getPorts() {

ports = CommPortIdentifier.getPortIdentifiers();

while (ports.hasMoreElements()) {

CommPortIdentifier curPort = (CommPortIdentifier) ports.nextElement();

if (curPort.getPortType() == CommPortIdentifier.PORT_SERIAL) {

portMap.put(curPort.getName(), curPort);

}

}

return portMap.keySet().toArray(new String[0]);

}

選択したポートへの接続:

public void connect() {

String selectedPort = (String)gui.ports.getSelectedItem();

selectedPortIdentifier = portMap.get(selectedPort);

CommPort commPort;

try{

commPort = selectedPortIdentifier.open("UART controller", TIMEOUT);

serialPort = (SerialPort)commPort;

serialPort.setSerialPortParams(BAUD_RATE, SerialPort.DATABITS_8, SerialPort.STOPBITS_1, SerialPort.PARITY_NONE);

gui.writeLog(selectedPort + " opened successfully.");

}catch (PortInUseException e){

gui.writeLogWithWarning(selectedPort + " is in use. (" + e.toString() + ")");

}catch (Exception e){

gui.writeLogWithWarning("Failed to open " + selectedPort + " (" + e.toString() + ")");

}

}

データ転送プロセス:

public boolean writeData(byte[] bytes){

boolean successfull = false;

try {

gui.writeLog("WRITING: " + HexBinUtil.stringFromByteArray(bytes));

output.write(bytes);

output.flush();

successfull = true;

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to write data. (" + e.toString() + ")");

}

return successfull;

}

データ受信中:

public void serialEvent(SerialPortEvent serialPortEvent) {

if (serialPortEvent.getEventType() == SerialPortEvent.DATA_AVAILABLE) {

try {

byte singleData = (byte)input.read();

gui.writeLog("READING: " + HexBinUtil.stringFromByteArray(singleData));

}

catch (Exception e) {

gui.writeLogWithWarning("Failed to read data. (" + e.toString() + ")");

}

}

}

すでに述べたように、DAC / ADCは、有効な8ビット値の書き込みコマンドをドキュメントに記載されている特定のレジスタアドレスに送信することによって制御されます。レジスターの現在の状態を判別するには、読み取りコマンドを送信し、要求されたレジスターのアドレスを指定する必要があります。ドキュメントにいつもあるように完全な説明。

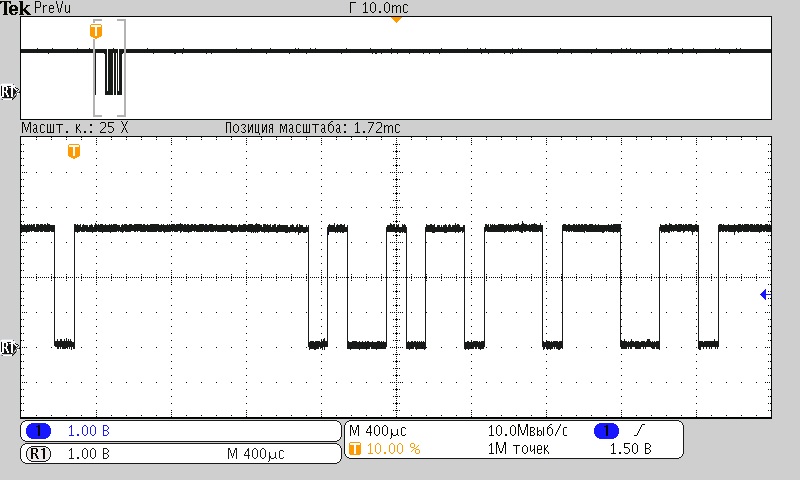

UARTデータ送信

AD9993-EBZを調査する過程で、使用可能な12ビットのレジスタアドレス空間で使用されるデータビットは8つだけであることがわかりました。また、レジスタ状態の送信値は8ビットで表されます。データ転送のタイプ(書き込み/読み取り)を決定するには、1データビットを転送する必要があります。

UARTインターフェイスを介したメッセージの最大サイズに対する現在の制限は8データビットであるため、書き込みプロセス中に3つの連続する8ビットメッセージを送信し、読み取りプロセス中に2つのメッセージを送信することにしました。

最初のパッケージには、パッケージサイズ全体で複製されたデータ送信のタイプが含まれます。したがって、可能な値は2つだけです。読み取りの場合は00000000、書き込みの場合は11111111です。受信信号のさらなる処理を簡素化するために、1つのデータビットの送信に整数バーストを使用しました。

次に、要求されたレジスタのアドレスと、記録プロセス中のレジスタ状態の送信値が送信されます。

開発したUARTパッケージのオシログラム

ユーザーインターフェース

ソフトウェアユーザーインターフェイスの主な要素は、使用可能なシリアルポートに接続/切断するためのボタン(要素3、4)、アドレスとレジスタ値を入力するためのフィールド(要素7、8)、ログウィンドウ(要素6)です。このソフトウェアは、「ポートに接続されている」と「ポートから切断されている」という2つの状態で対話するように設計されています。状態は、プログラムインターフェイス上のいくつかの要素のアクティビティを決定し、エラーや誤ったソフトウェアの使用の可能性を減らすために、特定のメソッドの実行を制限します。有効にすると、プログラムは「ポートから切断された」状態になります。また、プログラムの操作を容易にするために(私はプロジェクトの主な目標の1つでした)、JSON形式ですでに保存されているコマンドを使用してファイルを接続する機能が追加されました(要素10)。

コマンドのロードプロセス:

ファイル選択

コマンドインターフェイスこの

機能を使用すると、ロードされたコマンドをセクション(要素12)に並べ替えたり、接続されたコマンドを操作するプロセスをカスタマイズしたりできます(押すとすぐにコマンドをシリアルポートに送信するか、選択したコマンドに従ってアドレスフィールドと値フィールドに入力するか)。 ..。

FPGA用プロジェクトの開発

一般情報

FPGAのプロジェクトの開発を開始する前に、彼が解決しなければならないタスクを決定する必要があります。

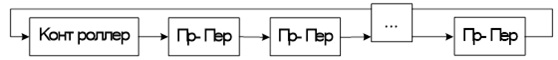

これは次のように聞こえます。FPGAのプロジェクトは、次のデータ変換をサポートする必要があります。データ変換

図

DE10-Nanoは、UARTインターフェイスのTxラインから信号(上部信号)を受信します。次に、FPGAは、それぞれ8ビットの3つのメッセージから受信データを正しく判別し、それらをドキュメントに対応するSPIメッセージ形式(4行で表示)に変換する必要があります。

この変換を実装するために必要な主なモジュールは、UARTコントローラーモジュールとSPIコントローラーモジュールです。章の残りの部分が割り当てられるのは彼らです。

FPGAのプロジェクトを開発する際には、IDE Qartus Prime LiteEditionの第17バージョンが使用されました。

Quartusの使用経験がない場合、またはFPGAをまったくプログラムしていない場合は、 Quartusの最初のプロジェクトの理解しやすい(私の意見では)例から始めることをお勧めします。

以下に説明するVerilogコードからのすべての抜粋は、インターネット上で見つかったソリューションをまとめたものであり、独創性を装うものではないことに注意してください。繰り返しますが、このプロジェクトの主な目標は、特定の問題を解決することです。

UARTコントローラー

説明

UARTコントローラーは、次の3つのモジュールで構成されています。

- パルスジェネレータ;

- 記録モジュール;

- 読み取りモジュール。

ほとんどの情報が得られたこの記事を参照 することをお勧めします。これからは、(私の意見では)最も重要な実装の詳細のみに焦点を当てます。

パルスジェネレータ

UARTインターフェイスは非同期であるため、受信者は、送信された信号を正しく受信するために独自の参照信号を生成する必要があります。これにより、新しいビットの情報の始まりを正しく判断できます。

標準的なUARTボーレートの一般的に受け入れられている範囲があります:300; 600; 1200; 2400; 4800; 9600; 19200; 38400; 57600; 115200; 230400; 460800; 921600ボー この場合、データ転送は9600ボーで発生します。次に、シンボルレートの16倍の周波数のジェネレーターを取得する必要があります。これは、送信信号のレベルを正しく検出するために必要です。

パルスを生成するために、50MHzのジェネレーターがチップ上で使用されます。希望の周波数を得るには、発電機の325番目のパルスごとに考慮する必要があります。

Verilogでは次のようになります。

input Clk; // 50

input Rst_n; //

input [15:0] BaudRate; // , 325

output Tick; //

reg [15:0] baudRateReg; //

always @(posedge Clk or negedge Rst_n)

if (!Rst_n) baudRateReg <= 16'b1;

else if (Tick) baudRateReg <= 16'b1;

else baudRateReg <= baudRateReg + 1'b1;

assign Tick = (baudRateReg == BaudRate);

endmodule

リーダーモジュール

リーダーは、RXラインからの入力信号を出力8ビットデータアレイに変換します。

読み取ったデータを直接読み取って出力に転送します。

input Clk, Rx,Tick; // 50, Rx,

input [3:0]NBits; // , 8

output RxDone; //

output [7:0]RxData; //

reg read_enable = 1'b0; //

reg RxDone = 1'b0; //

reg [3:0] counter = 4'b0000; //

reg start_bit = 1'b1; //

reg [4:0]Bit = 5'b00000; //

reg [7:0] RxData; //

reg [7:0] Read_data= 8'b00000000; //

always @ (posedge Tick) //

begin

if (read_enable)

begin

RxDone <= 1'b0; //

counter <= counter+1'b1; //

if ((counter == 4'b1000) & (start_bit)) //

begin

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits)) //

begin

Bit <= Bit+1'b1;

Read_data <= {Rx,Read_data[7:1]};

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits) & (Rx)) //

begin

Bit <= 4'b0000;

RxDone <= 1'b1; //

counter <= 4'b0000; //

start_bit <= 1'b1; //

end

end

end

always @ (posedge Clk)

begin

if (NBits == 4'b1000) // 8 ,

begin

RxData[7:0] <= Read_data[7:0];

end

end

伝送モジュール

伝送モジュールは、8ビットの入力信号をUARTシリアルデータパケットに変換します。

直接データ転送:

input Clk, Rst_n, TxEn; // 50, ,

input Tick; //

input [3:0]NBits; //

input [7:0]TxData;

output Tx;

output TxDone;

reg Tx;

reg TxDone = 1'b0;

reg write_enable = 1'b0;

reg start_bit = 1'b1;

reg stop_bit = 1'b0;

reg [4:0] Bit = 5'b00000;

reg [3:0] counter = 4'b0000;

reg [7:0] in_data=8'b00000000;

always @ (posedge Tick) //

begin

if (!write_enable)

begin

TxDone = 1'b0;

start_bit <=1'b1;

stop_bit <= 1'b0;

end

if (write_enable)

begin

counter <= counter+1'b1; //

if(start_bit & !stop_bit)//

begin

Tx <=1'b0;

in_data <= TxData;

if ((counter == 4'b1111) & (start_bit) ) //

begin

start_bit <= 1'b0;

in_data <= {1'b0,in_data[7:1]};

Tx <= in_data[0];

end

if ((counter == 4'b1111) & (!start_bit) & (Bit < NBits-1)) //

begin

in_data <= {1'b0,in_data[7:1]};

Bit<=Bit+1'b1;

Tx <= in_data[0];

start_bit <= 1'b0;

counter <= 4'b0000;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (!stop_bit)) //

begin

Tx <= 1'b1;

counter <= 4'b0000;

stop_bit<=1'b1;

end

if ((counter == 4'b1111) & (Bit == NBits-1) & (stop_bit) ) //

begin

Bit <= 4'b0000;

TxDone <= 1'b1;

counter <= 4'b0000;

//start_bit <=1'b1;

end

end

end

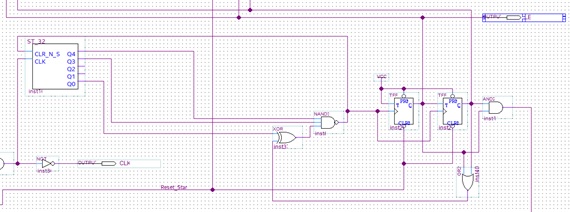

SPIコントローラー

重要な逸脱

FPGAに基づいて実装されたSPIコントローラーはUARTコントローラーよりも複雑な論理構造であるため、コントローラーの回路モデルで操作ロジックの詳細な説明を実行する方が簡単です。

コントローラの一般的なスキーム

開発されたモデルは、3つの主要なモジュールに分けることができます。

- シーケンシャル書き込みモジュール。

- ビットカウンターモジュール;

- エラーアナライザモジュール。

回路は使用される要素間の接続性が高いため、モジュールへの分割はかなり任意です。分割は、一般的な図に示されている要素の個々のグループによって実行されるタスクに基づいています。

回路のクロッキングは、CLK_125ラインを介して供給される12.5MHz信号によって提供されます。

制御メッセージの形成に関するコントローラーの作業の開始は、「START」信号によって実行されます。この信号により、回路のすべてのモジュールが初期状態に設定され、SPIインターフェースの出力ラインCLK、SS、MOSIで必要な信号を生成するサイクルの開始が初期化されます。

シーケンシャル書き込みモジュール

シリアル書き込みモジュールは、SPIコントローラーの主なタスク、つまり、シリアルMOSIラインへのパラレルビットデータの出力を実行します。これは、D-flip-flopsに基づくシフトレジスタの原理で動作するRG_24_PI_SO要素によるものです。

RG_24_PI_SO要素には、SPI送信形式のAD9993-EBZドキュメントに対応する24のデータ入力があります。それらが含まれます:

- コマンドデータ(DATA_0 – DATA_7);

- アドレスデータを登録します(ADR_0 – ADR_12);

- W / R書き込み/読み取りモードビット。

提示された信号は、LoadP_ShiftN入力の論理レベル「1」で並列に書き込まれます。さらに、LoadP_ShiftN入力の論理レベル「0」では、CLK入力の各クロックサイクルで、エレメントは記録されたデータをMOSI出力のシリアルラインに交互に再生します。

ビットカウンターモジュール

ビットカウンタモジュールは、SPIインターフェイスのSSラインでのデータ書き込みイネーブル信号の持続時間を決定するために必要です。 AD9993-EBZのドキュメントによると、イネーブル信号の持続時間は送信データの合計持続時間と等しくなければならないため、データ送信の開始から24の同期パルスをカウントして、イネーブル信号の必要な持続時間を決定する必要があります。カウント機能はST_32エレメントによって実行されます。ST_32エレメントは、24番目のクロック信号が検出されると、カウンターをリセットするため、および送信されたイネーブル信号を終了するために使用される信号を再生します。

主な機能に加えて、ビットカウンタモジュールはエラー分析プロセスの初期化も担当します。その初期アクションは、最後に記録されたレジスタのアドレスに値の読み取りコマンドを送信することです。最後に送信されたデータビットが送信された瞬間(実験的に確立された)から23同期パルスの持続時間に相当する時間間隔の後にエラー分析プロセスを開始する必要があるため、リセット信号後のビットカウンターは23同期パルスカウントモードに切り替わり、エラー分析プロセスの動作が保証されます。

エラー分析モジュール

前のモジュールの説明で述べたように、エラー分析の機能を提供するために、データ記録プロセスで使用されるレジスタアドレスでICに格納されたコマンドの値を読み取ることに基づく方法が開発されました。読み取りプロセスは、書き込まれた値を読み取られたデータと比較して不整合を識別し、したがって発生したエラーを判別するために必要です。エラー分析モジュールは、シフトレジスタの原理で動作するRG_8_SI_PO要素に基づいています。このエレメントは、MISOシリアルポートを介して受信した信号をパラレル8ビット出力に変換します。次に、データは、データ記録プロセス中に使用されたコマンドの値と比較されます。比較機能は、exclusive-orロジックに基づいてCMP_8要素によって実行されます。不一致が見つかった場合、モジュールはLED出力に信号を送信します。LED出力は次のデータ記録プロセスまで論理ユニットの状態になります。 LED出力はLEDの1つに関連付けられ、そのグループはDE10 Nano開発ボードに存在し、発生したエラーを視覚的に通知すると想定されています。

結論

この問題を解決した結果、PCとDAC / ADCデバイス間の相互作用のスキームが設計され、いくつかの重要な利点を備えて物理的に実装されました。実装の過程で、FPGAとPCの接続に関する問題が解決されました。これに対する解決策は、外部UARTモジュールを使用することでした。PC用のソフトウェアはJava言語で書かれています。このソフトウェアは、開発されたUART送信形式でデータを送受信するための基本機能を備えたインターフェースを備えており、さらに、保存されたコマンドをロードする機能も備えています。FPGAベースのUARTおよびSPIコントローラーが開発されました。

このプロジェクトの枠組みの中で検討されている問題により、次のことが可能になります。

- 集積回路と外部デバイスとの相互作用の方法を評価します。

- FPGAをマッチングデバイス、データ交換用のバッファとして使用する方法を評価します。

- 実用的なソフトウェアを開発するための最も効果的なアプローチの1つを探ります。

PS私は、間違いの追加、発言、および兆候があれば喜んでいます。