安価なラップトップであれ、数百万ドルのサーバーであれ、あらゆるコンピューターのすべての中央処理装置には、キャッシュと呼ばれるデバイスがあります。そして、非常に高い確率で、いくつかのレベルがあります。

それはおそらく重要です、そうでなければなぜそれをインストールするのですか?しかし、キャッシュは何をするのでしょうか、そしてなぜそれは異なるレベルを持っているのですか?そして、「12ウェイセットアソシアティブ」とはどういう意味ですか?

キャッシュとは何ですか?

TL; DR:これは、CPUの論理ブロックのすぐ近くにある、小さいながらも非常に高速なメモリです。

ただし、もちろん、キャッシュについてさらに多くのことを学ぶことができます...

架空の魔法のストレージシステムから始めましょう。これは、無限に高速で、無限の数のデータ転送を同時に処理でき、常にデータを安全に保ちます。もちろん、近くにはそのようなものはありませんが、そうであれば、プロセッサの構造ははるかに単純になります。

理論上のストレージシステムは必要なすべての番号を即座に送受信できるため、プロセッサには、加算、乗算などの論理ブロックとデータ送信制御システムのみが必要になります。データが転送されるのを待つ間、ロジックブロックをアイドル状態にする必要はありません。

しかし、私たちが知っているように、そのような魔法のストレージ技術はありません。代わりに、ハードドライブまたはソリッドステートドライブがあり、それらの最高のものでさえ、最新のプロセッサに必要な処理機能をはるかに下回っています。

ストレージ

の優れた機能この理由は、最新のプロセッサは非常に高速であるためです。2つの64ビット整数を追加するのに必要なクロックサイクルは1つだけです。プロセッサが4GHzで実行されている場合、これはわずか0.00000000025秒、つまり1/4ナノ秒です。

同時に、回転するハードディスクは、ディスク上のデータを見つけるためだけに数千ナノ秒かかり、ディスクを転送することは言うまでもなく、ソリッドステートドライブは数十または数百ナノ秒かかります。

明らかに、そのようなドライブを内部に組み込むことはできませんプロセッサなので、それらの間には物理的な分離があります。したがって、データを移動するための時間が追加され、状況が悪化します。

残念ながら、これはデータストレージの優れ

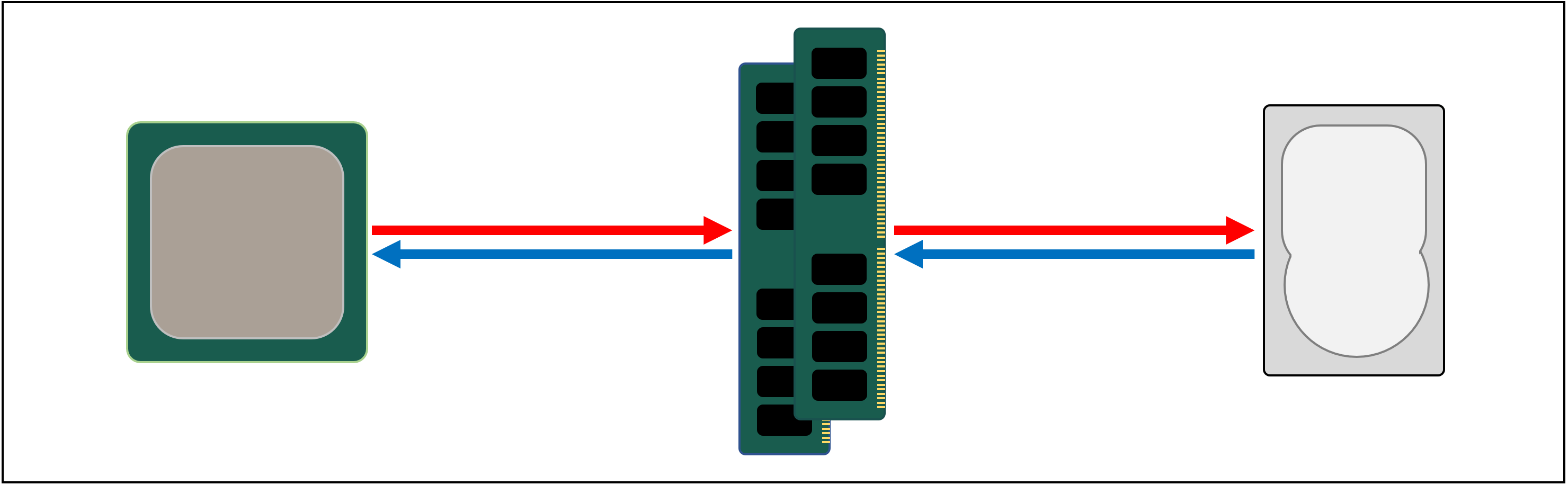

た機能です。そのため、プロセッサとメインドライブの間に別のストレージシステムを配置する必要があります。ストレージデバイスよりも高速で、複数のデータ転送を同時に処理でき、プロセッサにはるかに近い必要があります。

まあ、私たちはすでにそのようなシステムを持っています、そしてそれはRAMと呼ばれています;すべてのコンピューターに存在し、まさにこのタスクを実行します。

そのようなストレージのほとんどすべてがDRAM (動的ランダムアクセスメモリ)タイプです。これらは、どのストレージデバイスよりもはるかに高速にデータを転送できます。

ただし、その驚異的な速度にもかかわらず、DRAMはそのような量のデータを保存することができません。Micron

の最大のDDR4メモリチップのいくつかは、32 Gbps、つまり4GBのデータを格納します。最大のハードドライブは4,000倍以上を保存します。

そのため、データネットワークの速度を上げましたが、プロセッサで処理できるように、限られた量のDRAMにどのデータを保存するかを判断するために、追加のシステム(ハードウェアとソフトウェア)が必要になります。

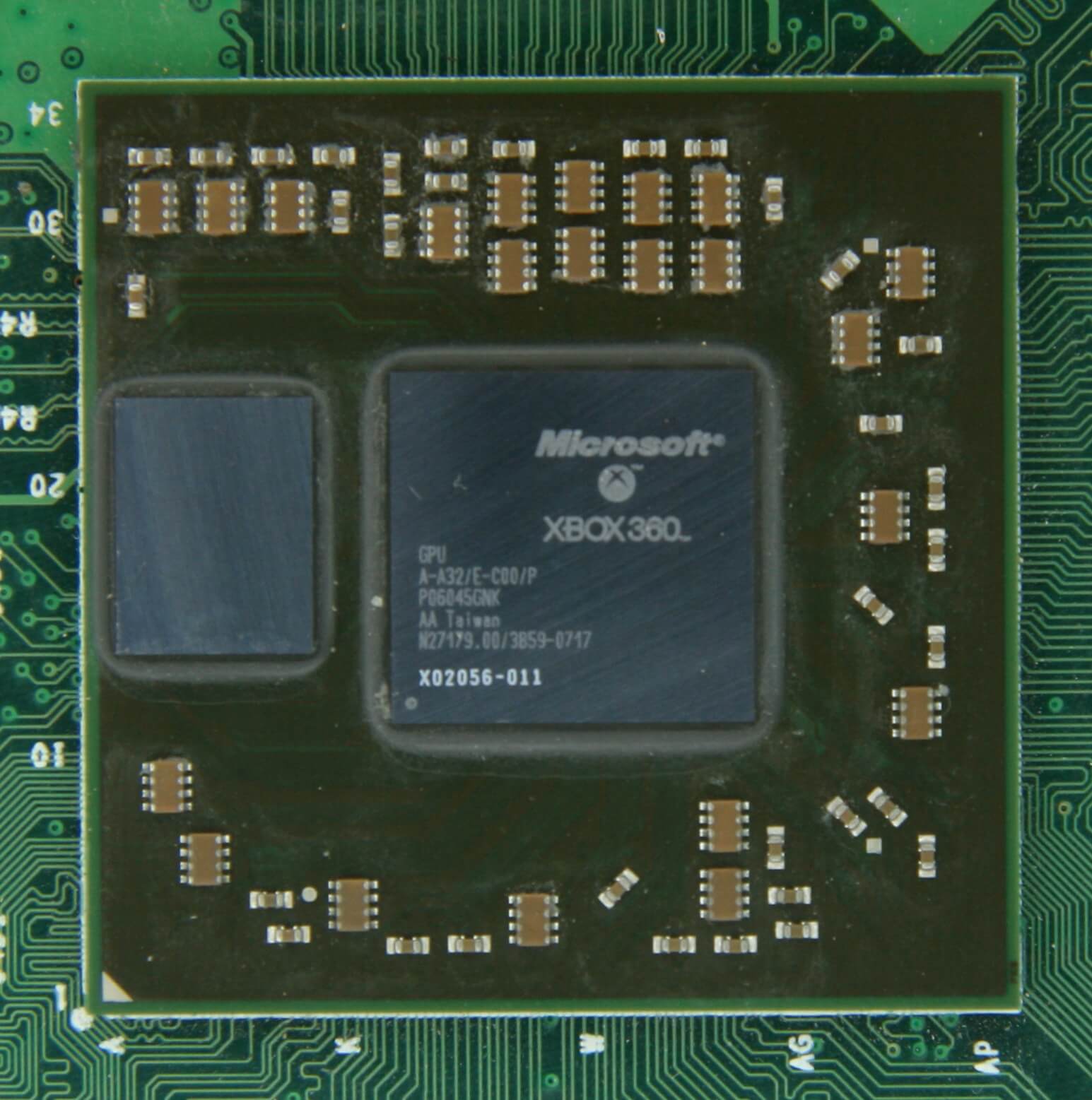

DRAMを製造することができるで(これは埋め込みDRAMと呼ばれる)、チップ・パッケージ。ただし、プロセッサは非常に小さいため、大量のメモリを収容することはできません。

Xbox 360 GPUの左側にある10MBのDRAM。出典:CPU Grave Yard

DRAMの大部分は、プロセッサのすぐ近くにあり、マザーボードに接続されており、常にプロセッサに最も近いコンポーネントです。ただし、このメモリはまだ十分な速度ではありません...

DRAMはデータを見つけるのに約100ナノ秒かかりますが、少なくとも1秒あたり数十億ビットを転送することができます。 CPUブロックとDRAMブロックの間に配置できる別のメモリステージが必要なようです。

残りのステージがシーンに表示されます:SRAM(静的ランダムアクセスメモリ)。 DRAMは微細なコンデンサを使用してデータを電荷の形で保存しますが、SRAMは同じタスクにトランジスタを使用します。トランジスタはプロセッサの論理ブロックと同じ速度(DRAMの約10倍)で動作します。

もちろん、SRAMには欠点があり、スペースと関係があります。

トランジスタメモリはDRAMよりもはるかに多くのスペースを占有します。4GBのDDR4チップと同じサイズで、100MB未満のSRAMを取得できます。ただし、CPUと同じ製造プロセスを使用して製造されるため、SRAMは、論理ブロックのできるだけ近くで、プロセッサ内に直接埋め込むことができます。

追加のステップごとに、保存されたボリュームを犠牲にして、転送されるデータの速度を上げました。先に進んで新しいステップを追加できます。これは高速ですが、小さくなります。

そして、より厳密な定義に到達しましたキャッシュの概念:プロセッサ内にあるSRAMのコレクション。非常に高速でデータを転送および保存することにより、プロセッサの使用率を最大化します。この定義に満足していますか?これからはもっと複雑になるので、素晴らしいです!

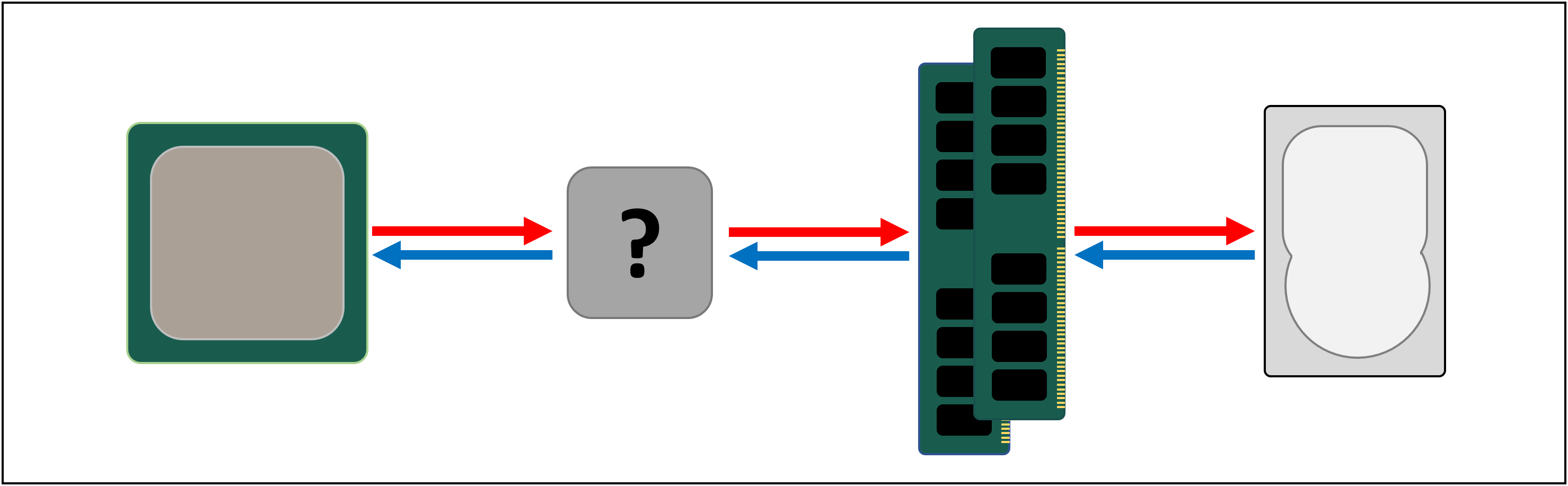

現金:マルチレベルパーキング

上で述べたように、プロセッサの論理ブロックのデータ消費を処理できる魔法のストレージシステムがないため、キャッシュが必要です。最新のCPUとGPUには、次の構造を持つ一連のキャッシュ内の階層に配置された多くのSRAMが含まれています。

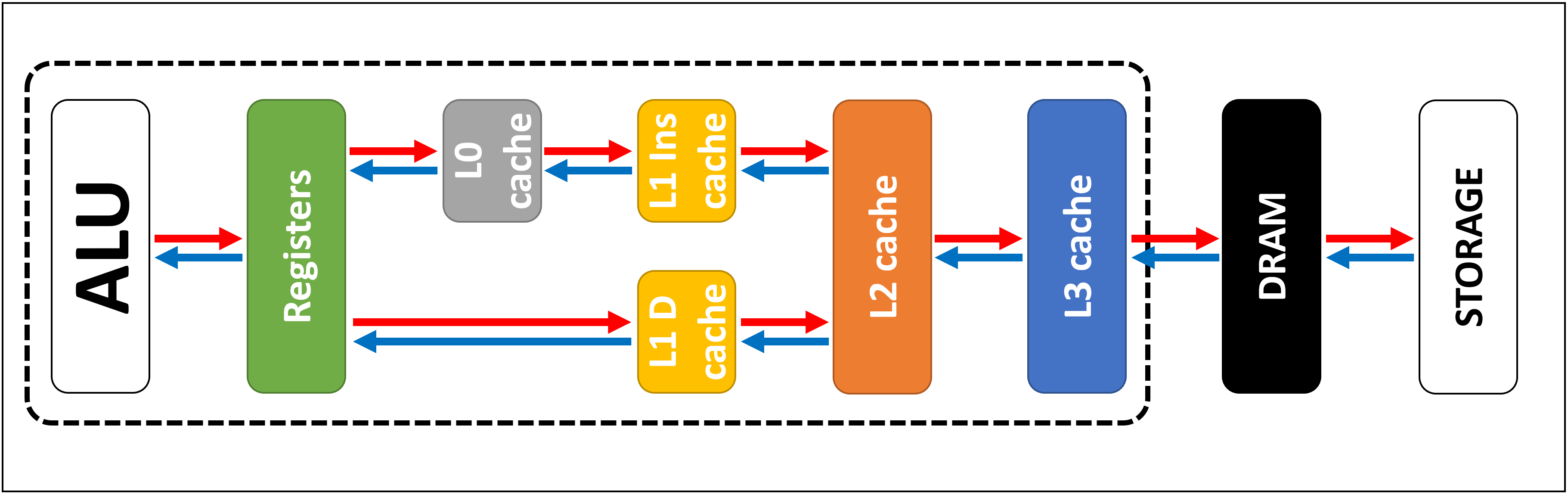

上の画像では、プロセッサ(CPU)は破線の長方形で示されています。左側はALU(算術論理ユニット)です。これらは、数学的な操作を実行する構造です。厳密にはキャッシュではありませんが、ALUに最も近いメモリレベルはレジスタです(レジスタファイルで順序付けられます)。

それぞれに1つの数値、たとえば64ビットの整数が格納されます。値自体は、一部のデータの要素、特定の命令のコード、またはその他のデータのメモリアドレスにすることができます。

デスクトッププロセッサのレジスタファイルは、たとえば、各Intel Corei9-9900Kコアでは非常に小さいです。このようなファイルには2つのバンクがあり、整数用のバンクには180個の64ビット整数しか含まれていません。ベクトル(数値の小さな配列)用の別のレジスタファイルには、168個の256ビット要素が含まれています。つまり、各コアの合計レジスタファイルは7KBよりわずかに少なくなります。比較のために、ストリーミングマルチプロセッサ用のNvidia GeForce RTX 2080 Tiレジスタファイル(GPUはCPUコアアナログを呼び出すため)のサイズは256KBです。

キャッシュと同様に、レジスタはSRAMですが、その速度は、それらが提供するALUの速度を超えることはありません。 1クロックサイクルでデータを転送します。ただし、大量のデータ(1つの要素のみ)を格納するようには設計されていないため、それらの隣には常に大きなメモリブロックがあります。これは、第1レベルのキャッシュ(レベル1)です。

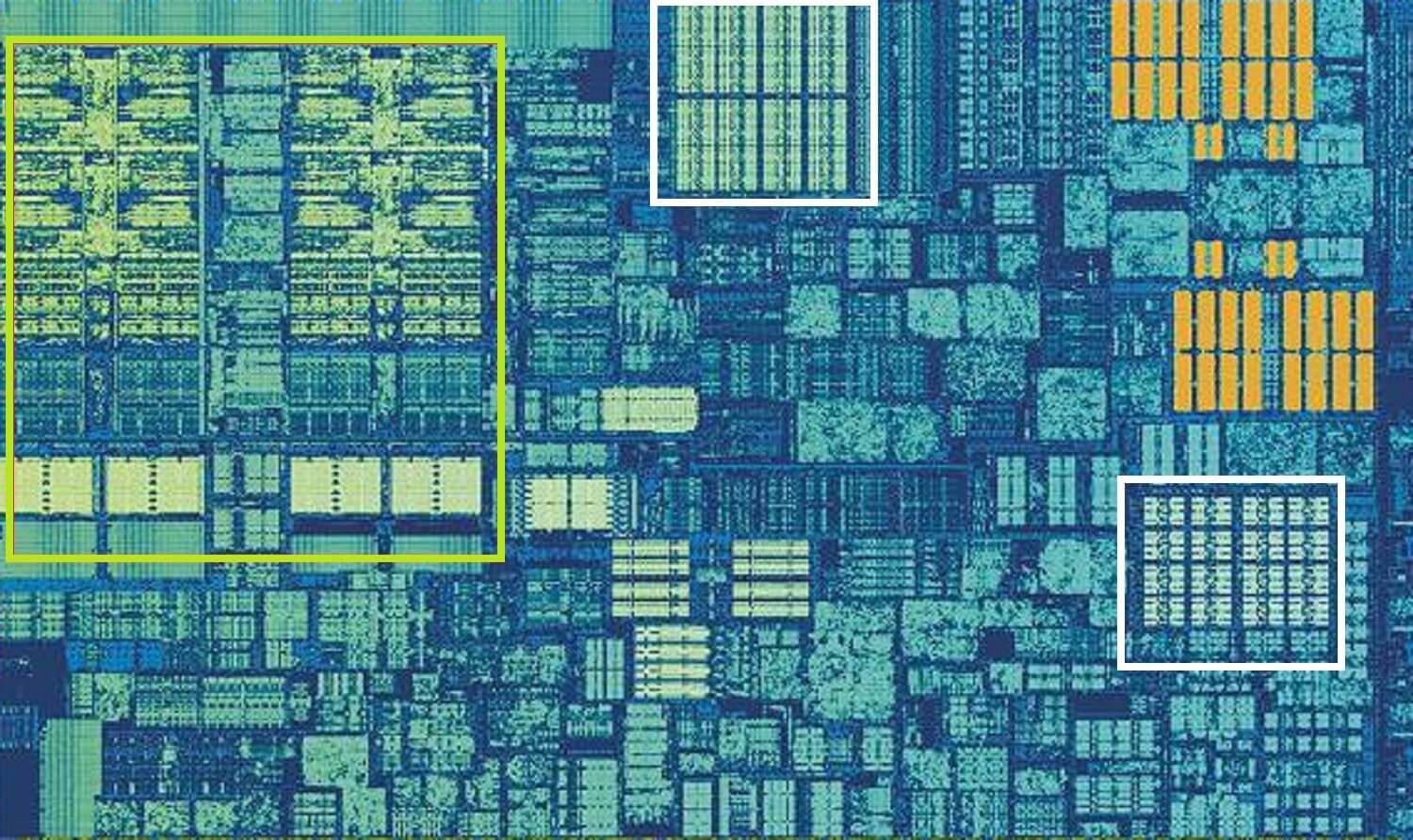

1つのIntelSkylakeプロセッサコア。出典:Wikichip

画像上ザは、Intelのコアの1つの拡大図であるSkylakeマイクロアーキテクチャのデスクトッププロセッサ。

ALUファイルとレジスタファイルは左側にあり、緑色の枠で囲まれています。写真の上部にあるレベル1データキャッシュは白で示されています。 32 KBの情報しか含まれていませんが、レジスタと同様に、論理ブロックの非常に近くに配置され、それらと同じ速度で動作します。

右側の別の白い長方形は、サイズが32KBのレベル1命令キャッシュを示しています。名前が示すように、小さなマイクロオペレーションに分割する準備ができているさまざまなコマンドを格納します。(通常はμopsで示されます)ALUが実行する必要があります。それらのキャッシュもあります。これは、L1キャッシュよりも小さく(1,500の操作のみを含む)、近いため、レベル0として分類できます。

なぜこれらのSRAMがこんなに小さいのか疑問に思われるかもしれません。なぜそれらはメガバイトのサイズではないのですか?データキャッシュと命令キャッシュを合わせると、チップ上のメインロジックブロックとほぼ同じ領域を占めるため、それらを増やすと、ダイの総領域が増加します。

ただし、サイズが数キロバイトになる主な理由は、メモリ容量が増えると、データの検索と取得に必要な時間が長くなるためです。 L1キャッシュは非常に高速である必要があるため、サイズと速度の間にはトレードオフがあります。このキャッシュからデータを取得するには、せいぜい約5クロックサイクルかかります(浮動小数点値の場合はさらに多くなります)。

SkylakeのL2キャッシュ:256KB SRAM

しかし、これがプロセッサ内の唯一のキャッシュである場合、そのパフォーマンスは予期しないハードルにぶつかるでしょう。そのため、カーネルには別のメモリ層が組み込まれています。レベル2キャッシュです。これは、命令とデータを含む一般化されたストレージブロックです。

それは、常にレベル1よりも大きくなっている:AMDに禅2つのプロセッサ、それは低レベルのキャッシュのための十分なデータを提供するために、512キロバイトまでかかります。ただし、サイズが大きい場合は犠牲が必要です。レベル1と比較して、このキャッシュからデータを見つけて転送するのに約2倍の時間がかかります。

最初のIntelPentiumの時代には、レベル2キャッシュは別のチップであり、別の小さなボード(DIMM RAMなど)にインストールされるか、メインのマザーボードに組み込まれていました。徐々に、それはプロセッサ自体のケースに移動し、最終的にはチップクリスタルに完全に統合されました。これは、PentiumIIIやAMDK6-IIIなどのプロセッサの時代に起こりました。

この成果の直後に、より低いレベルをサポートするために必要な別のレベルのキャッシュが続き、マルチコアチップの全盛期にちょうど間に合うように到着しました。

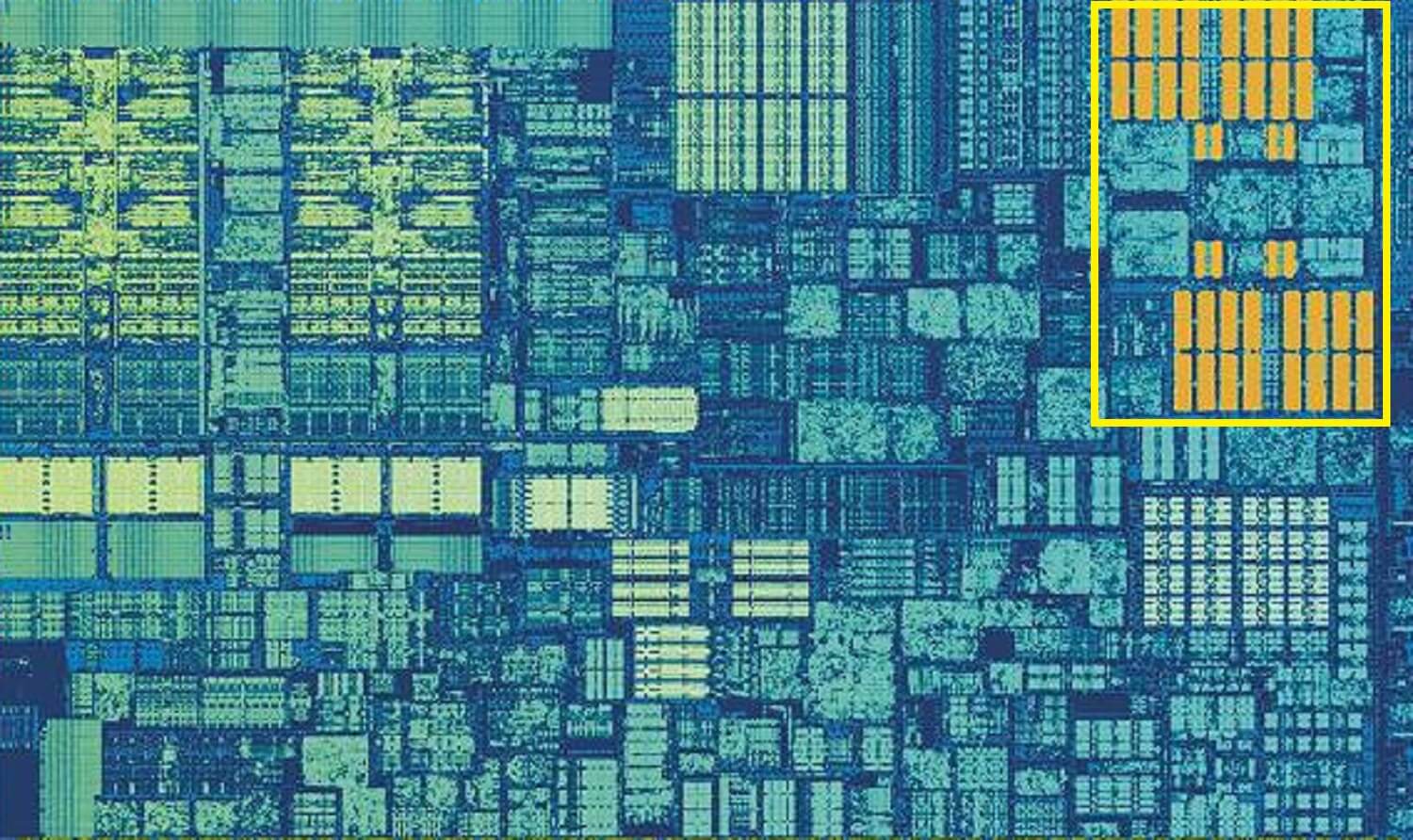

Intel KabyLakeチップ。出典:Wikichip

このIntel Kaby Lakeチップの画像は、左側に4つのコアを示しています(統合されたGPUはダイのほぼ半分を占め、右側にあります)。各コアには、レベル1および2のキャッシュの独自の「個人用」セット(白と黄色のボックスで強調表示)がありますが、SRAMブロックの3番目のセットもあります。

3番目のレベルのキャッシュ(レベル3)は、1つのコアのすぐ隣にありますが、他のすべてのコアに完全に共通です。各コアは、別のコアのL3キャッシュの内容に自由にアクセスできます。これははるかに大きい(2〜32 MB)が、はるかに遅く、平均30サイクルを超えます。特に、カーネルが遠くのキャッシュブロックにあるデータを使用する必要がある場合はそうです。

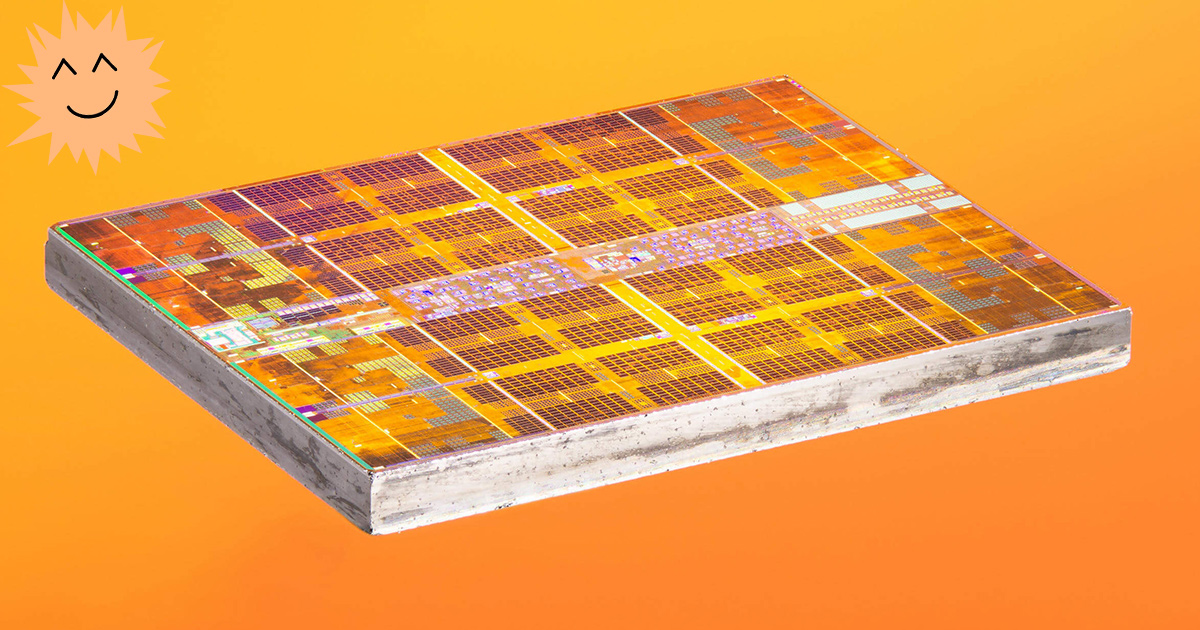

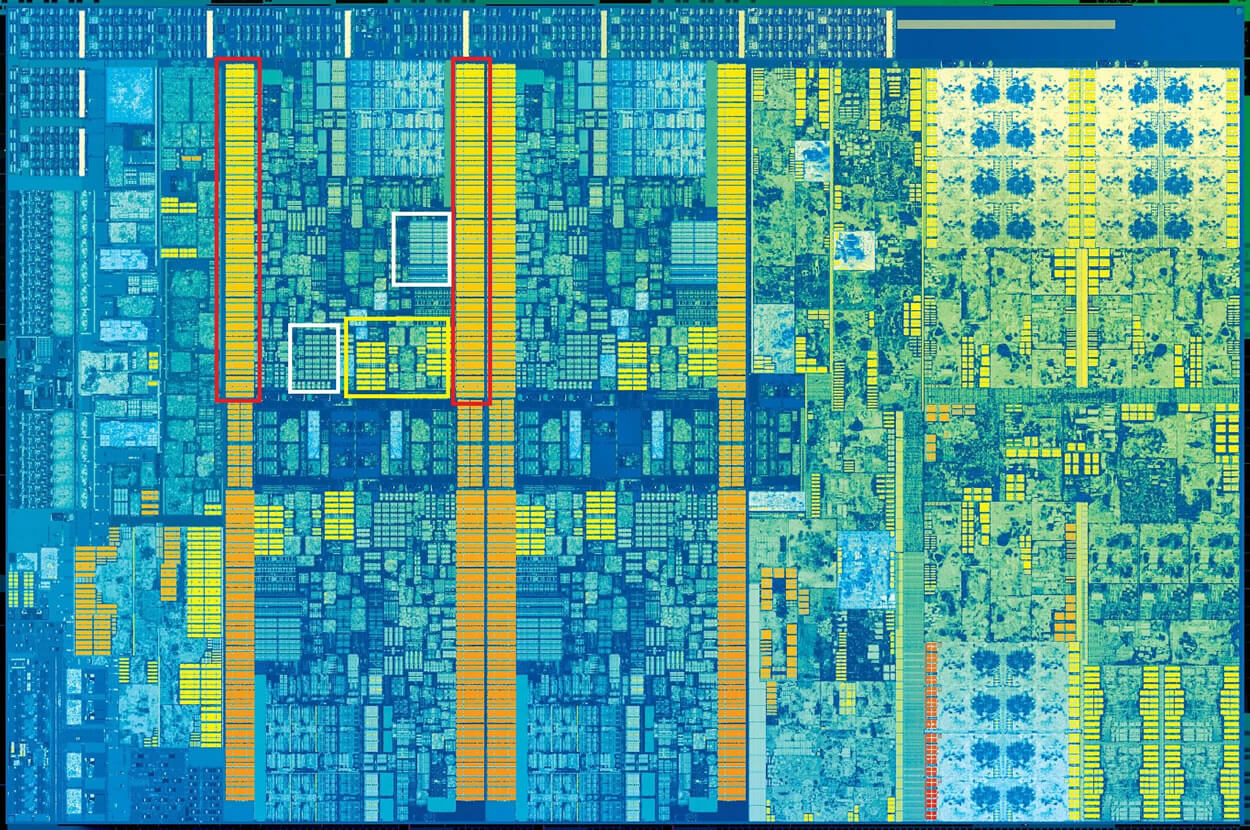

以下に示すのは、AMD Zen 2アーキテクチャの1つのコアです。32KBのレベル1データおよび命令キャッシュ(白いボックス)、512KBのレベル2キャッシュ(黄色のボックス)、および巨大な4MBのL3キャッシュブロック(赤いボックス)です。

AMD Zen 2プロセッサのシングルコアにズームインしました。出典:Fritzchens Fritz

しかし、待ってください。32KBが512KBよりも多くの物理スペースを占めるにはどうすればよいでしょうか。レベル1に保存されるデータが非常に少ない場合、L2およびL3キャッシュと比較して不均衡に大きいのはなぜですか?

数字だけでなく

キャッシュは、論理ブロックへのデータの転送を高速化し、頻繁に使用される命令とデータのコピーを近くに保持することにより、パフォーマンスを向上させます。キャッシュに保存される情報は、データ自体と、システムメモリ/ストレージに最初に配置されていた場所の2つの部分に分けられます。このアドレスは、キャッシュタグと呼ばれます。

プロセッサがメモリとの間でデータの読み取りまたは書き込みを行う必要がある操作を実行すると、レベル1キャッシュ内のタグをチェックすることから始まります。必要なデータが存在する場合(キャッシュヒットが発生した場合)、このデータはほぼすぐに。キャッシュミスは、必要なタグがキャッシュの最下位レベルで見つからない場合に発生します。

L1キャッシュに新しいタグが作成され、残りのプロセッサアーキテクチャが引き継ぎ、キャッシュの他のレベル(必要に応じてメインストレージまで)でそのタグのデータを探します。ただし、この新しいタグ用にL1キャッシュのスペースを解放するには、L2に何かをスローする必要があります。

これにより、データがほぼ一定にシャッフルされ、わずか数クロックサイクルで実行されます。これを実現する唯一の方法は、データ管理を処理するためにSRAMの周りに複雑な構造を作成することです。言い換えると、プロセッサコアが1つのALUのみで構成されている場合、L1キャッシュははるかに単純になりますが、それらは数十個あるため(そして、それらの多くは2つの命令ストリームとジャグリングします)、キャッシュはデータを移動するために多くの接続を必要とします。

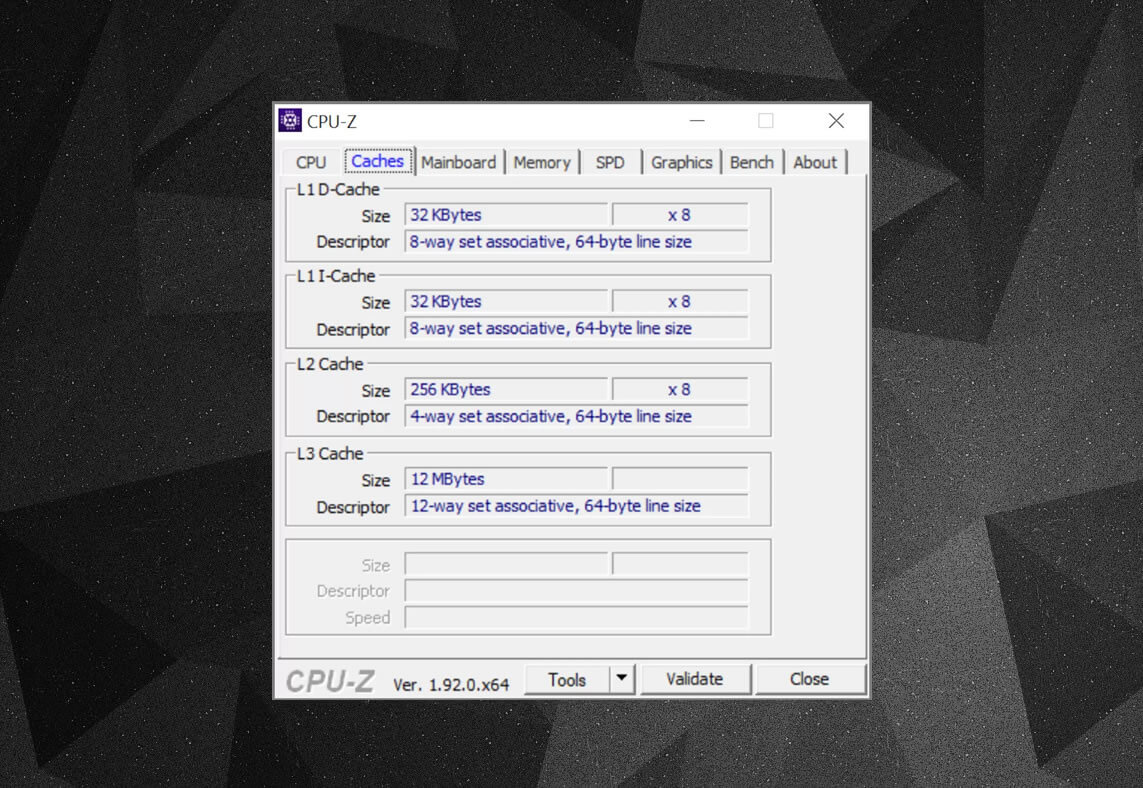

CPU-Z などの無料ソフトウェアを使用して、コンピューターのプロセッサーのキャッシュ情報を調べることができます。しかし、このすべての情報はどういう意味ですか?重要な要素は、システムメモリからキャッシュにデータのブロックをコピーするために使用されるルールを示すセットアソシアティブラベルです。

上記のキャッシュ情報は、Intel Corei7-9700K用です。レベル1の各キャッシュは、セットと呼ばれる64個の小さなブロックに分割され、これらの各ブロックもキャッシュラインに分割されます。(サイズは64バイト)。 「セットアソシアティブ」とは、システムからのデータのブロックが1つの特定のセットのキャッシュラインにバインドされ、他の場所に自由にバインドできないことを意味します。

「8ウェイ」とは、1つのブロックをセット内の8つのキャッシュラインに関連付けることができることを意味します。関連付けレベルが高いほど(つまり、「ウェイ」が大きいほど)、プロセッサのルックアップ中にキャッシュがヒットする可能性が高くなり、キャッシュミスによる損失が少なくなります。このようなシステムの欠点は、データのブロックごとにより多くのキャッシュラインを処理する必要があるため、複雑さと消費電力が増加し、パフォーマンスが低下することです。

包括的キャッシュL1 + L2、ビクティムキャッシュL3、ライトバックポリシー、ECCもあります。出典:Fritzchens Fritz

キャッシュの複雑さの別の側面は、異なる層間でデータがどのように保存されるかに関係しています。ルールは包含ポリシーで設定されます。たとえば、IntelCoreプロセッサには完全に包括的なL1 + L3キャッシュがあります。これは、たとえば、レベル1の一部のデータがレベル3に存在する可能性があることを意味します。貴重なキャッシュスペースの浪費のように見えるかもしれませんが、プロセッサが下位レベルのタグを見逃した場合でも、必要がないという利点があります。トップレベルでデータを検索します。

同じプロセッサでは、L2キャッシュは包括的ではありません。そこに格納されているすべてのデータが他のレイヤーにコピーされることはありません。これによりスペースが節約されますが、チップのメモリシステムはL3(常にはるかに大きい)で欠落しているタグを探します。被害者キャッシュは原則として似ていますが、下位レベルから運ばれる情報を格納するために使用されます。たとえば、AMD Zen 2プロセッサは、L2からのデータを格納するだけのビクティムキャッシュL3を使用します。

キャッシュとメインシステムメモリの両方にデータを書き込むなど、他のキャッシュポリシーがあります。これらは書き込みポリシーと呼ばれます。最新のプロセッサのほとんどは、ライトバックキャッシュを使用しています-これは、データがキャッシュレイヤーに書き込まれるときに、そのコピーをシステムメモリに書き込む前に遅延が発生することを意味します。ほとんどの場合、この一時停止は、データがキャッシュに残っている限り続きます。RAMは、キャッシュから「ポップ」された場合にのみこの情報を受け取ります。

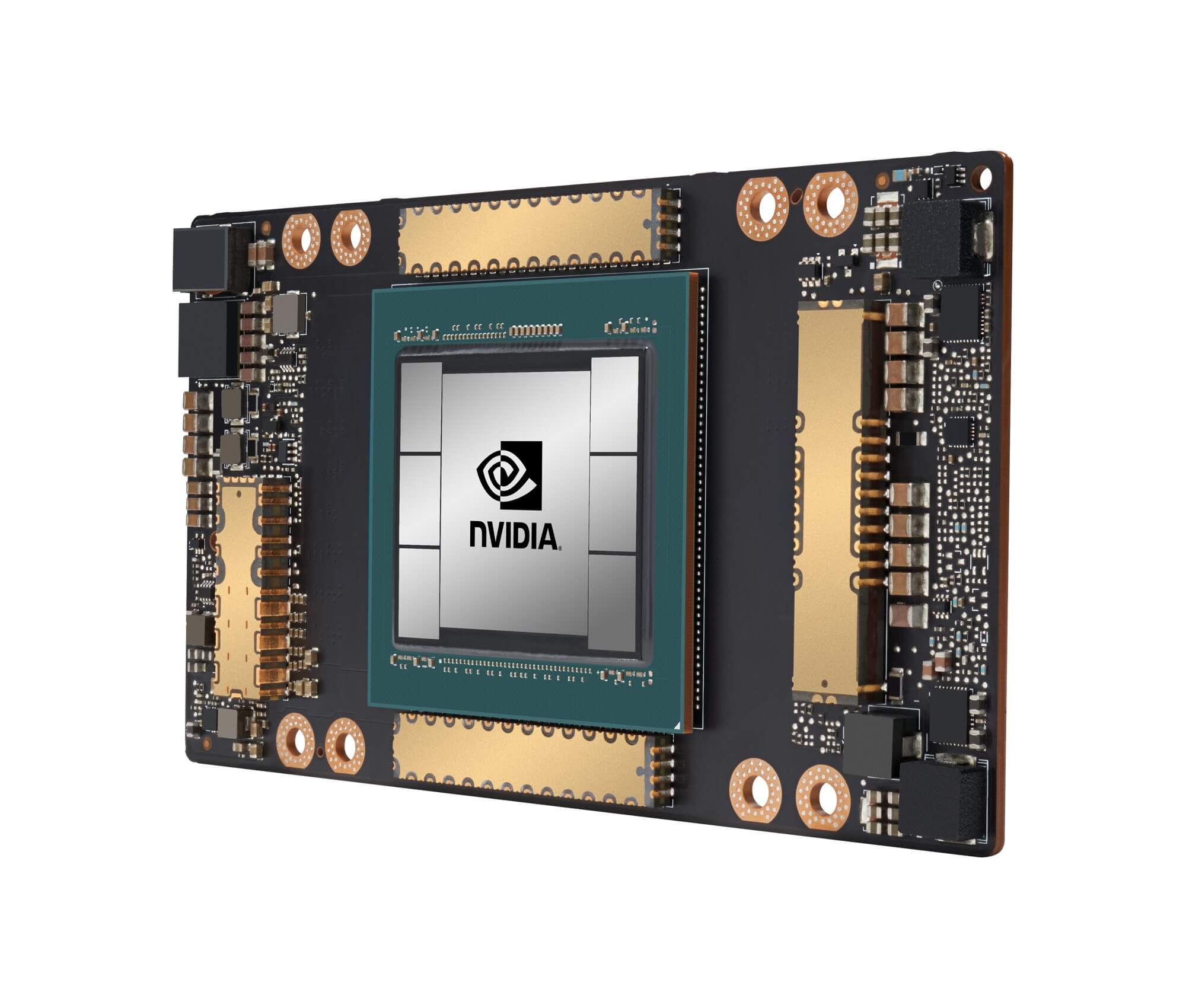

20 MBL1キャッシュと40MBL2キャッシュを備えたNvidiaGA100 GPU

プロセッサ設計者にとって、キャッシュサイズ、タイプ、およびポリシーの選択は、ドライブのバランスを取り、複雑さとチップフットプリントの増加に伴ってプロセッサパワーを向上させることです。マンハッタンの領域を占有しないように(そして同じ量の電力を消費しないように)1000チャネルの20MBレベル1連想キャッシュを作成することが可能である場合、そのようなチップを備えたコンピューターがすべてあります!

最新のプロセッサのキャッシュの最低レベルは、過去10年間ほとんど変更されていません。ただし、レベル3キャッシュのサイズは増え続けています。 10年前にInteli7-980Xで999ドルを持っていた場合、12MBのキャッシュを持つことができます。今日はその半分の金額64MBで購入できます。

要約すると、キャッシュは絶対に不可欠で素晴らしいデバイスです。CPUとGPUの他のタイプのキャッシュ(たとえば、連想変換バッファーやテクスチャキャッシュ)については説明していませんが、それらはすべて同じ単純な構造とレベルのレイアウトを持っているため、理解するのは難しくありません。

マザーボードにL2キャッシュを備えたコンピューターがありますか?スロット付きのPentiumIIとCeleron(例:300a)のドーターボードはどうですか?最初の共有L3プロセッサを覚えていますか?

広告

当社は、IntelおよびAMDのプロセッサを搭載したレンタルサーバーを提供しています。後者の場合、これらは壮大なサーバーです!AMD EPYCを搭載したVDS、最大3.4GHzのCPUコア周波数。最大構成は、128 CPUコア、512 GB RAM、4000 GBNVMeです。