8086には80を超えるラッチがあります。それらのいくつかは、ADピン(アドレス/データ)または制御ピンの値を格納します。その他は、マイクロコードとマイクロコードの現在のアドレス、およびマイクロコードルーチンからの戻りアドレスを格納します。 3つ目は、ソースおよび出力コマンドレジスタのビットと、コマンドのALU操作を格納します。多くは内部状態のステータスを保存しますが、私はまだ理解しています。

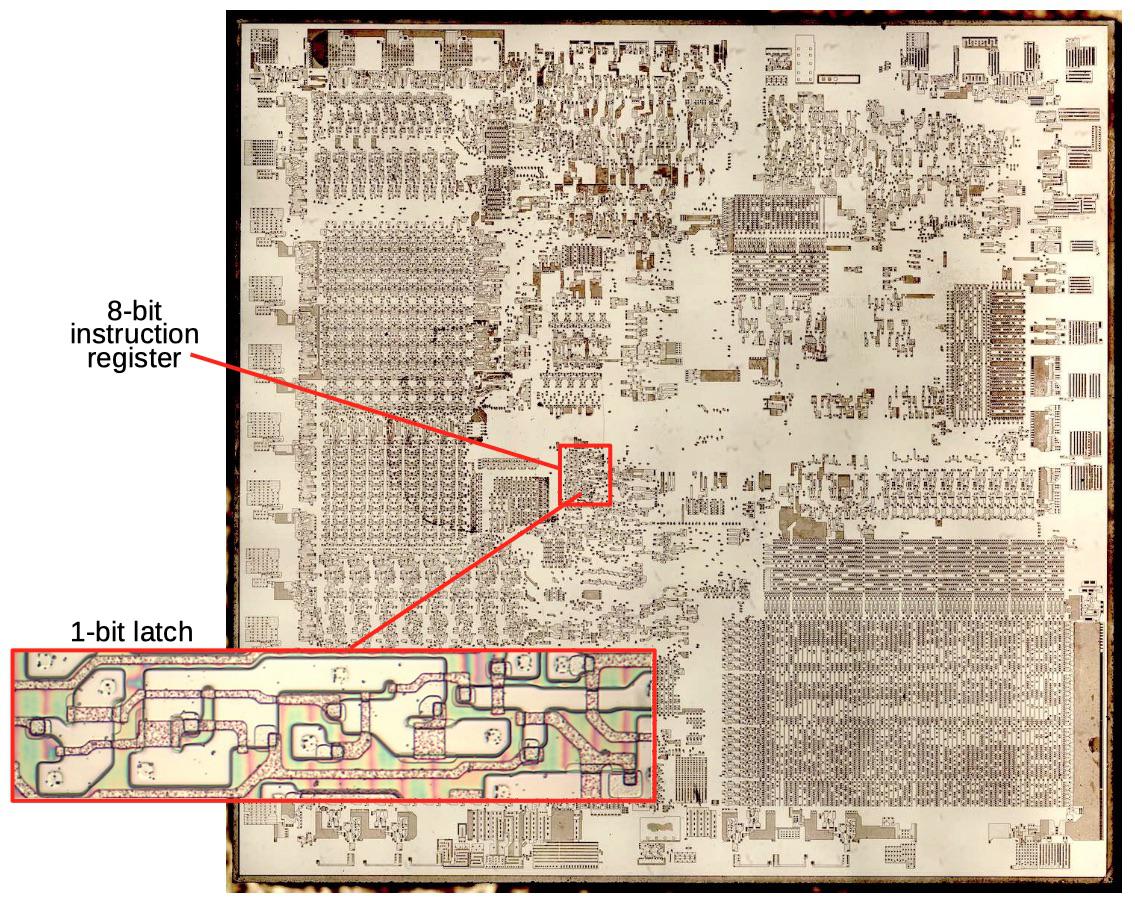

8ビット命令レジスタを

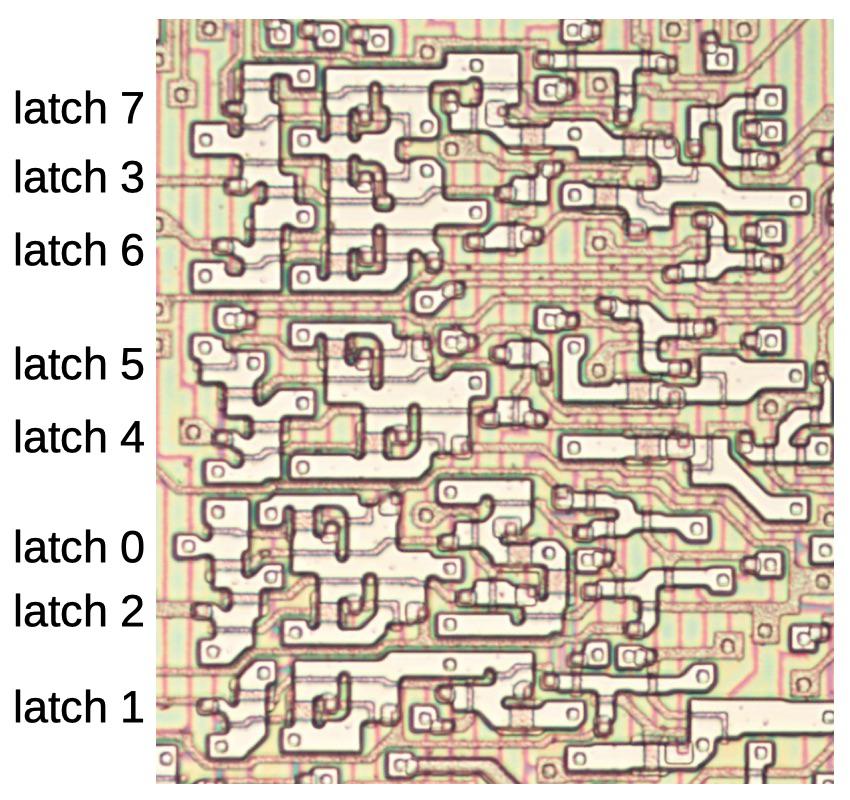

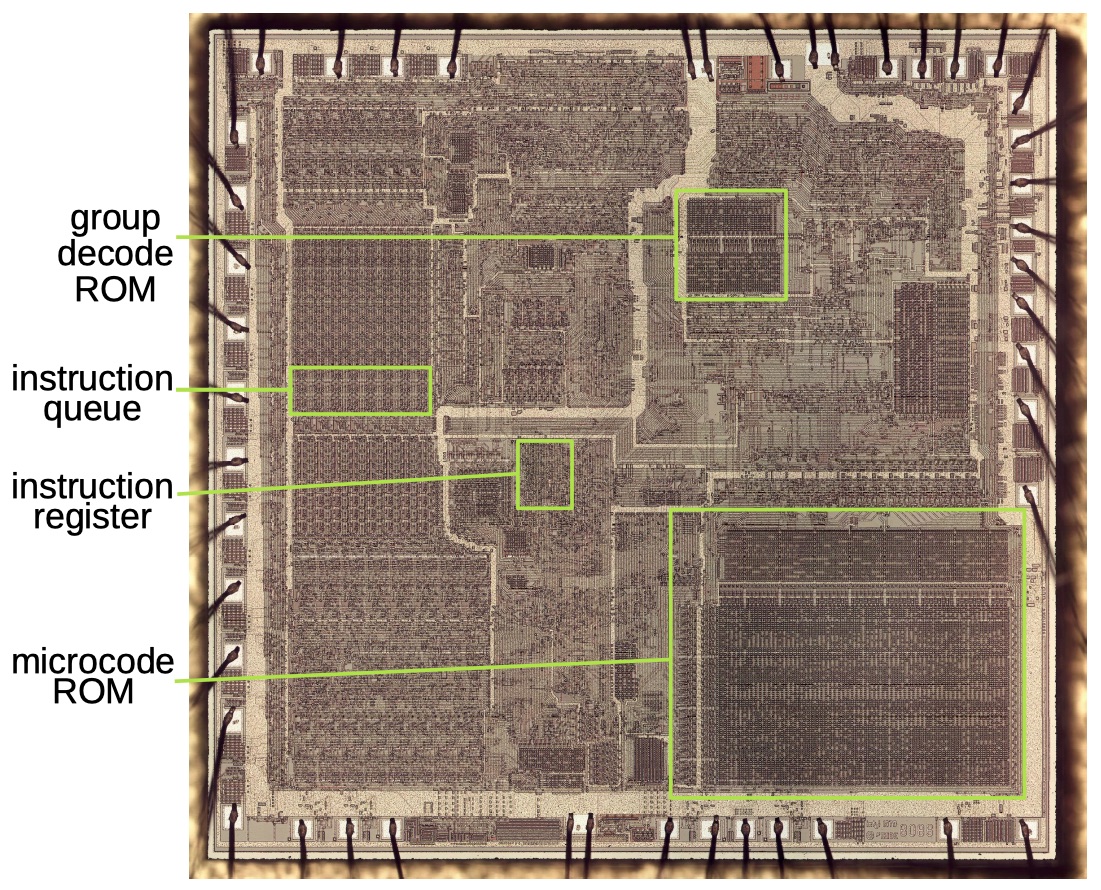

示すCrystal86上の写真は、顕微鏡下での8086シリコンダイを示しています。トランジスタが見えるように、金属層とポリシリコン層を削除しました。合計で約29,000個あります。割り当てられた領域には、8つのラッチで構成される8ビットのコマンドバッファが含まれています。この1978年のプロセッサは、単一の8ビットレジスタが比較的大きな領域を占めるのに十分なほど単純でした。拡大図は、単一のラッチを構成するシリコンとトランジスタを示しています。

ダイナミックラッチのしくみ

ラッチはプロセッサの動作を追跡するため、8086の最も重要な要素の1つです。ラッチはさまざまな方法で実行できます。 8086は、ダイナミックラッチと呼ばれるコンパクトな回路を使用しています。ダイナミックラッチは、その時代のマイクロプロセッサを制御するためによく使用されていた2相クロックジェネレータの動作に依存しています。 2相クロックは、順番にアクティブになる2つのクロック信号を生成します。最初のフェーズでは、メインクロックがハイで、付随するクロックがローです。それから彼らは場所を変えます。このサイクルは、クロック周波数、たとえば5MHzで繰り返されます。

多くのマイクロプロセッサは、NANDゲートを使用してRSフリップフロップを形成します。 RSフリップフロップは通常、動的ラッチよりも多くのスペースを占有します。特に、クロック周波数を維持するために追加の回路が追加されている場合はそうです。 Dトリガー(遅延トリガー)も人気がありますが、さらに複雑になり、6つのゲートを使用します。多くの場合、パストランジスタで十分です。 1クロックサイクルの値を保存できますが、長期保存は提供しません。

プロセッサには、可能な限り最高のクロック速度が常に選択されます。最初の8086は最大5MHzで動作し、その後8086-1は最大10MHzをサポートしました。ただし、動的ロジックを使用しているため、8086の最小クロック周波数は2MHzです。クロックジェネレータの動作が遅いと、回路がアクセスする前に導体から電荷が漏れてエラーが発生するリスクがあります。

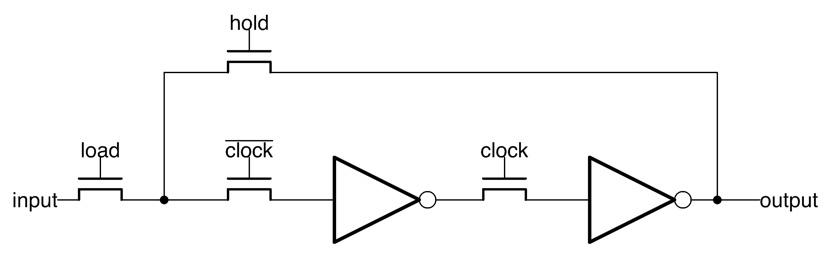

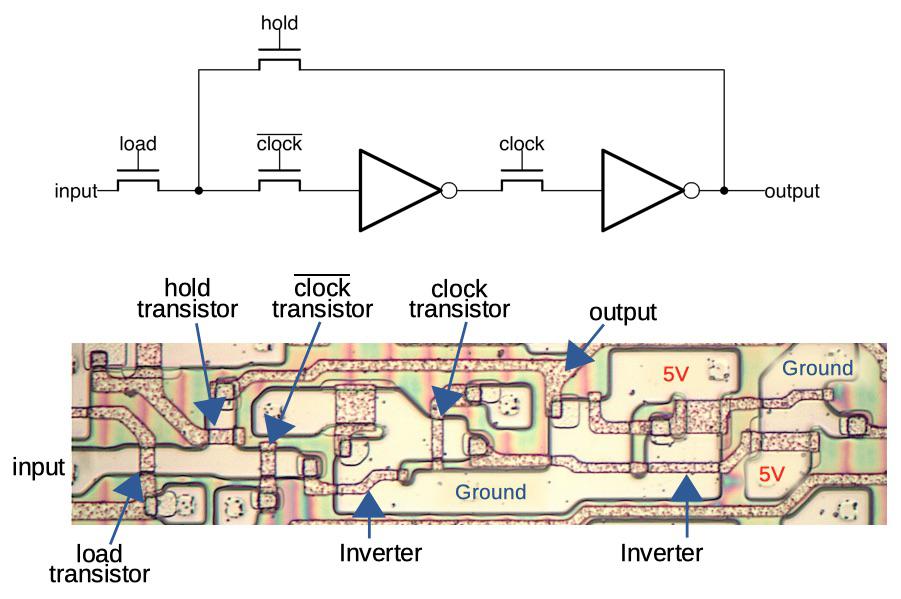

8086プロセッサのラッチは、4つのパストランジスタと2つのインバータで構成されています。ラッチは断続的なクロック信号で動作します。

上の図は、典型的な8086ラッチを示しています。これは、2つのインバーターといくつかのパストランジスターで構成されています。私たちの目的では、パストランジスタはスイッチと見なすことができます。1がゲートに来ると、トランジスタは信号をさらに送信します。 0が来ると、トランジスタは信号をブロックします。パストランジスタは、いくつかの信号によって制御されます。負荷。ラッチにビットをロードします。 hold(hold)、既存のビット値を保持します。最初のフェーズのクロックと2番目のフェーズのクロックが反転します。

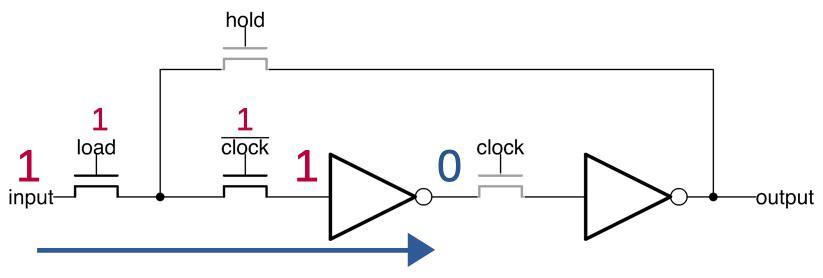

次の図は、値(この場合は1)がラッチにロードされる方法を示しています。負荷信号が上昇し、入力信号(1)がトランジスタを通過できるようになります。クロック信号以来ハイの場合、信号は2番目のトランジスタを通過してインバータに送られ、インバータは0を出力します。この時点で、3番目(クロック)のトランジスタが信号をブロックします。

負荷信号がハイになると、入力信号がラッチにロードされます。

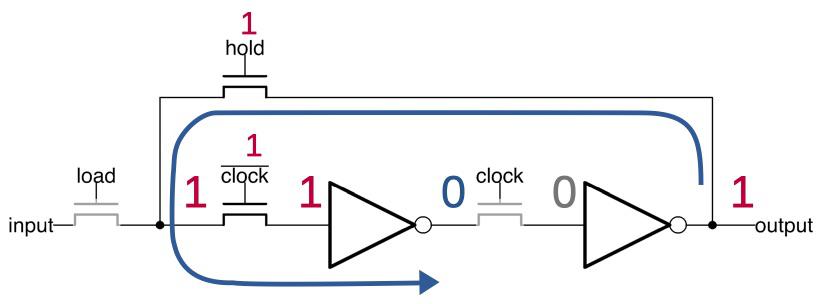

次のクロックフェーズでは、クロック信号がハイになり、0信号が2番目のインバーターに到達して1を出力します。ホールド信号がハイであるため、信号は戻りますが、クロックトランジスタによってブロックされます。..。この回路を動的にしているのは、現在、最初のインバーターに入力信号が送信されていないことです。回路の容量により、入力は1のままです(灰色で表示)。いつかこの電荷が漏れ、値が失われますが、その瞬間の前に、クロックパルスジェネレータの新しい切り替えが行われます。

クロック信号がハイになると、値は2番目のインバーターを通過します。最初のインバーター(灰色)への入力は、回路の容量によって維持されます。

クロックジェネレータの状態を切り替えた後、2番目のインバータへの入力が回路容量を提供します(以下を参照)。信号がフィードバックされ、最初のインバーターへの入力が再充電および更新されます。以降のクロックでは、ラッチはこのパターンと前のパターンを切り替え、保存された値を維持し、出力を安定させます。

ラッチの動作の鍵は、出力信号を安定に保つ2つのインバーターの存在です。奇数のインバーターは発振を引き起こします-この機能は8086チャージポンプによって使用されます。また、インバーターのペアはビットを格納するために8086レジスターのセットを使用します。ただし、レジスタのセットでは、2つのインバータが直接接続されており、クロック駆動のパストランジスタがないため、よりコンパクトですが、ストレージシステムの管理が困難になります。

クロック信号がハイの場合、値は最初のインバーターを通過します。

シリコンでの実装

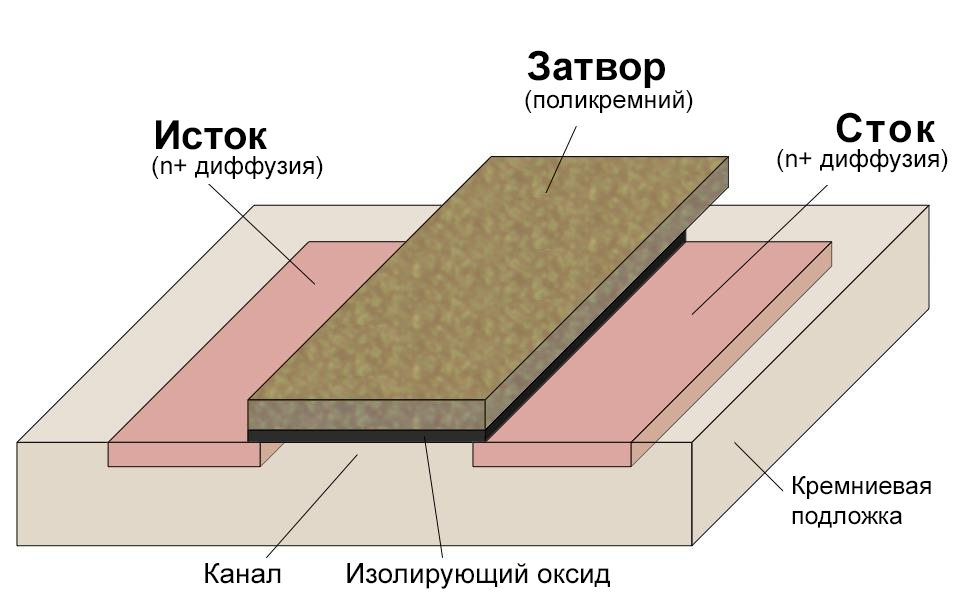

その時代の8086および他のプロセッサはN-MOSトランジスタに基づいていました。それらは、トランジスタを形成するドーピングプロセス中にヒ素またはホウ素不純物が添加されたシリコン基板から作られました。シリコンの上にはポリシリコンがあり、すべてのコンポーネントを接続するトランジスタと導体のゲートを作成しました。別の層である金属は、追加の導電性接続を提供しました。比較すると、最新のプロセッサは、N-MOSテクノロジーとP-MOSテクノロジーを組み合わせたCMOSテクノロジーを使用しており、複数の金属導電層を備えています。

N-MOSトランジスタ(MOS構造)をICに実装する方法

上の図は、トランジスタの構造を示しています。トランジスタは、あるセクション(ソース)から別のセクション(ドレイン)に電流を流すことを可能にするスイッチと考えることができます。トランジスタは、特殊なタイプのシリコン(ポリシリコン)で作られたゲートによって駆動されます。ゲートに電圧を印加すると、ソースとドレインの間に電流が流れ、ゲートを0Vに引くと電流がブロックされます。ゲートは、絶縁酸化物層によってシリコンから分離されています。このため、動的ラッチの例に見られるように、ゲートはコンデンサのように機能します。

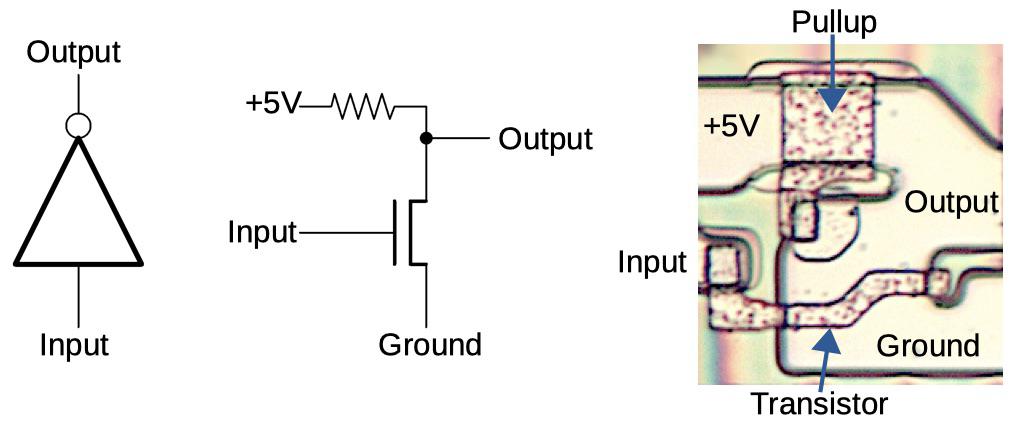

インバーター(下)は、N-MOSトランジスターと抵抗器で構成されています。信号が低い場合、トランジスタは無効になるため、プルアップ抵抗が出力信号を引き上げます。信号がハイになると、トランジスタがオンになり、出力をグランドに接続して出力をプルダウンします。したがって、回路は入力信号を反転します。

N-MOSゲートのプルアップ抵抗は、特殊なタイプのトランジスタを使用して実装されます。デプレッションモードトランジスタは抵抗のように機能しますが、占有するスペースが少なく、より効率的です。

この図は、トランジスタと抵抗でインバータを作成する方法を示しています。写真は、回路がチップにどのように実装されているかを示しています。金属層は除去され、ポリシリコンとシリコンが露出しています。

右の写真は、8086が物理的にインバーターを実装する方法を示しています。黄色がかった領域は不純物を含む導電性シリコンであり、斑点のある領域は上部のポリペプチドです。トランジスタは、ポリペプチドがドープされたシリコンと交差する場所で作られます。ポリシリコンはトランジスタのゲートを形成し、両側のシリコンのセクションがトランジスタのソースとドレインを提供します。大きなポリシリコン長方形は、+ 5Vと出力の間にプルアップ抵抗を形成します。これらの物理的構造の構造を図と比較できます。

次の図は、チップ上のラッチの実装を示しています。パススルートランジスタと2つのインバータがマークされています。最初のインバーターは上で説明されています。ポリシリコン導体は、コンポーネントを相互に接続します。追加の接続は、金属層によって提供されました(写真のために削除されました)。トランジスタの複雑な形状により、スペースを最も効率的に使用できます。

8086プロセッサのラッチの顕微鏡写真。導体のある金属層は除去されていますが、その痕跡は赤みがかった垂直線の形で表示されます。写真はレイアウトに合わせて180°回転しました。

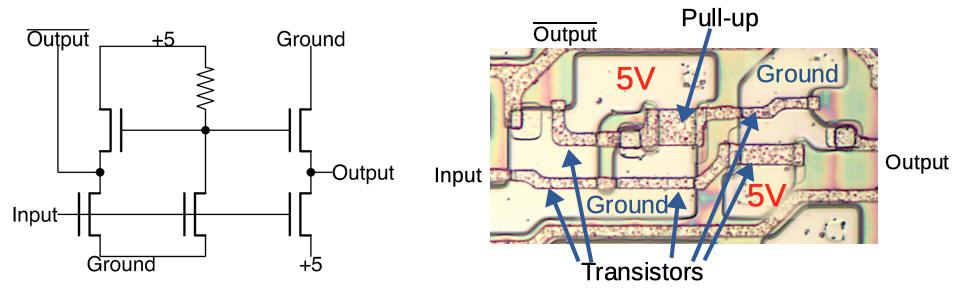

ラッチは、図にマークされていない出力バッファーを使用して、出力および反転出力に高電流信号を提供します。これらのバッファには、「スーパーバッファ」という面白い名前が付いています。これは、通常のN-MOSインバータよりもはるかに高い電流を供給するためです。 N-MOSインバーターの問題は、大容量の回路を駆動するときに動作が遅くなることです。スーパーバッファはより多くの電流を供給するため、信号をはるかに高速に切り替えます。これは、プルアップ抵抗をより高い電流のトランジスタに置き換えることによって実現されます。欠点は、プルアップトランジスタが動作するためにインバータを必要とするため、スーパーバッファ回路がより複雑になることです。したがって、スーパーバッファは必要な場合にのみ使用されます。通常、多くのゲートに信号を送信する場合、または長いバスを駆動する場合です。

スーパーバッファの8086ラッチ実装。+ 5Vとグランド接続が右端のトランジスタに移動していることに注意してください。

上の図は、8086ラッチスーパーバッファーの概略図を示しています。従来のスーパーバッファーとは異なり、これには反転スーパーバッファーと非反転スーパーバッファーの両方があります。回路を理解するために、中央の抵抗とトランジスタがインバータを形成することに注意してください。インバーター出力は上部トランジスターに接続され、非反転入力は下部トランジスターに接続されます。次に、入力が1の場合、下側のトランジスタがオンになり、入力が0の場合、インバータのおかげで、上側のトランジスタがオンになります。次に、入力が1の場合、下側のトランジスタが出力を引き上げ、対応する出力を引き下げます。入力が0の場合、上位のトランジスタが出力をプルダウンし、対応する出力をプルダウンします-アップ。

N-MOSインバーターの問題は、プルアップ抵抗の電流が制限されていることです。出力が0の場合、インバーターのトランジスターは、比較的高い電流で素早く出力を引き下げます。ただし、出力が1の場合、出力ははるかに弱いプルアップ抵抗によってプルアップされます。

スーパーバッファは、プルアップトランジスタとプルダウントランジスタを備えているという点でCMOSインバータに似ています。違いは、CMOSはP-MOSトランジスタとN-MOSトランジスタを使用するのに対し、P-MOSは反転ゲート入力を使用することです。逆に、N-MOSスーパーバッファーには別のインバーターが必要です。言い換えると、CMOSインバーターは2つのトランジスターを使用し、スーパーバッファーは4つのトランジスターを必要とするため、効率が大幅に低下します。

スーパーバッファは、プルアップにエンハンスメントモードトランジスタを使用し、プルダウンにエンハンスメントモードトランジスタを使用します。独自のチャネルを持つトランジスタのしきい値電圧はゼロ未満であるため、出力を5 Vまで引き上げることができ、それより低い電圧でオフにすることはできません。出力が低い場合でも、セルフチャネリングトランジスタはオンのままで、従来のインバータの通常のプルアップのように機能するため、特定の電流が流れます。スーパーバッファの詳細については、こちらをご覧ください。

コマンドレジスタ

ほとんどのプロセッサと同様に、8086には、現在実行中の命令が格納される命令レジスタがあります。 8086では、コマンドレジスタはコマンドの最初のバイト(複数のバイトにすることができます)を保持するため、8つのラッチで構成されます。それらは同一であると思われるかもしれませんが、それぞれが独自の形状を持っています。 8086のレイアウトは高度に最適化されているため、各ラッチの形状は、周囲の導体の制限により、利用可能なスペースを最大限に活用するように設計されています。特に、一部のラッチは相互に接続され、電源とアースを共有していることに注意してください。どうやら、同じ理由で、ラッチは一列に並んでいません。

8つのラッチはすべてわずかに異なる形状をしており、周囲の導体に合わせて最適化されています。記事の前半で、ラッチ#1を180°回転させました。赤い縦線は、除去された金属層の痕跡です。

チームは曲がりくねった道で8086を移動します。プロセッサは、パフォーマンスを向上させるプリフェッチを使用して、必要になる前にメモリから命令をロードします。これらは、一連のレジスタの中央にある6バイトのキューであるコマンドキューに格納されます。比較すると、最近のプロセッサには、数メガバイトにもなるコマンドキャッシュがあります。

コマンドが実行されると、チップのほぼ中央にあるコマンドレジスタに保存されます。比較的長い距離は、スーパーバッファーの必要性を説明しています。コマンドレジスタは、コマンドを「グループ復号化ROM」に送ります。このROMは、コマンドの高レベルの特性(シングルバイト、マルチバイト、またはコマンドプレフィックス)を定義します。そして、これは複雑な8086命令処理システムのほんの一部です。他のラッチは命令の一部を格納し、レジスタの使用法とALU操作をマークし、別の回路がマイクロコードエンジンを制御しますが、これについては個別に説明します。

Crystal 8086、コマンド処理の主要コンポーネントがマークされています。周囲に沿って、はんだ付けワイヤーがクリスタルを外部接点に接続します。

結論

8086は、動的ラッチを広範囲に使用して内部状態を格納します。それらは顕微鏡で見ることができ、それらの回路を追跡して理解することができます。最新のプロセッサとは異なり、そのトランジスタは顕微鏡で見るのに十分な大きさであるため、8086結晶は分析するのに興味深いものです。それは当時29,000のトランジスタを備えた洗練されたプロセッサでしたが、回路をトレースして理解するのに十分シンプルでした。