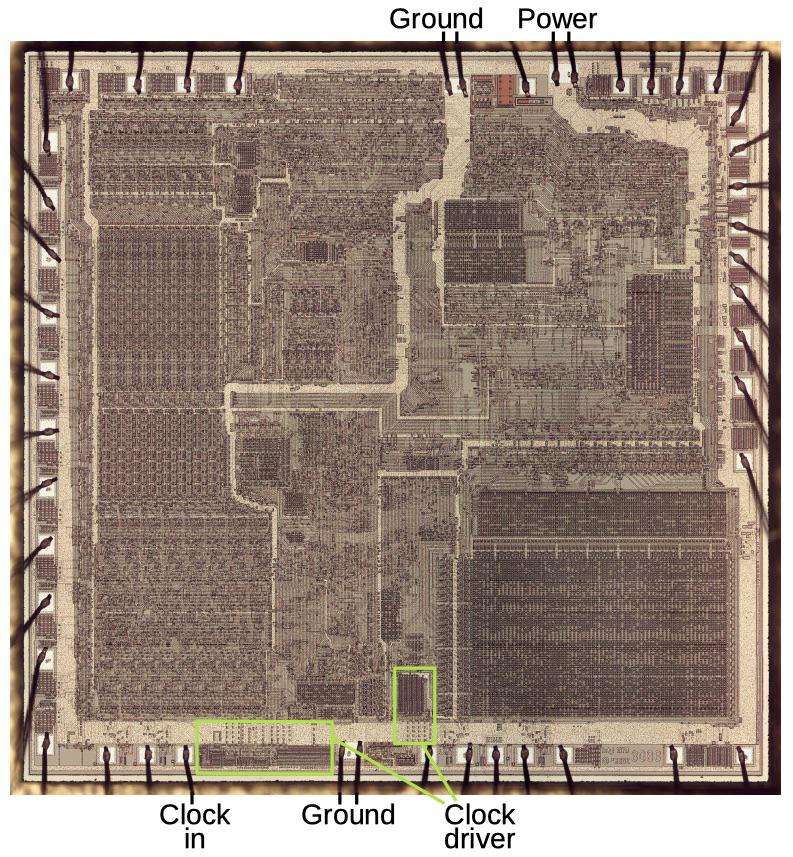

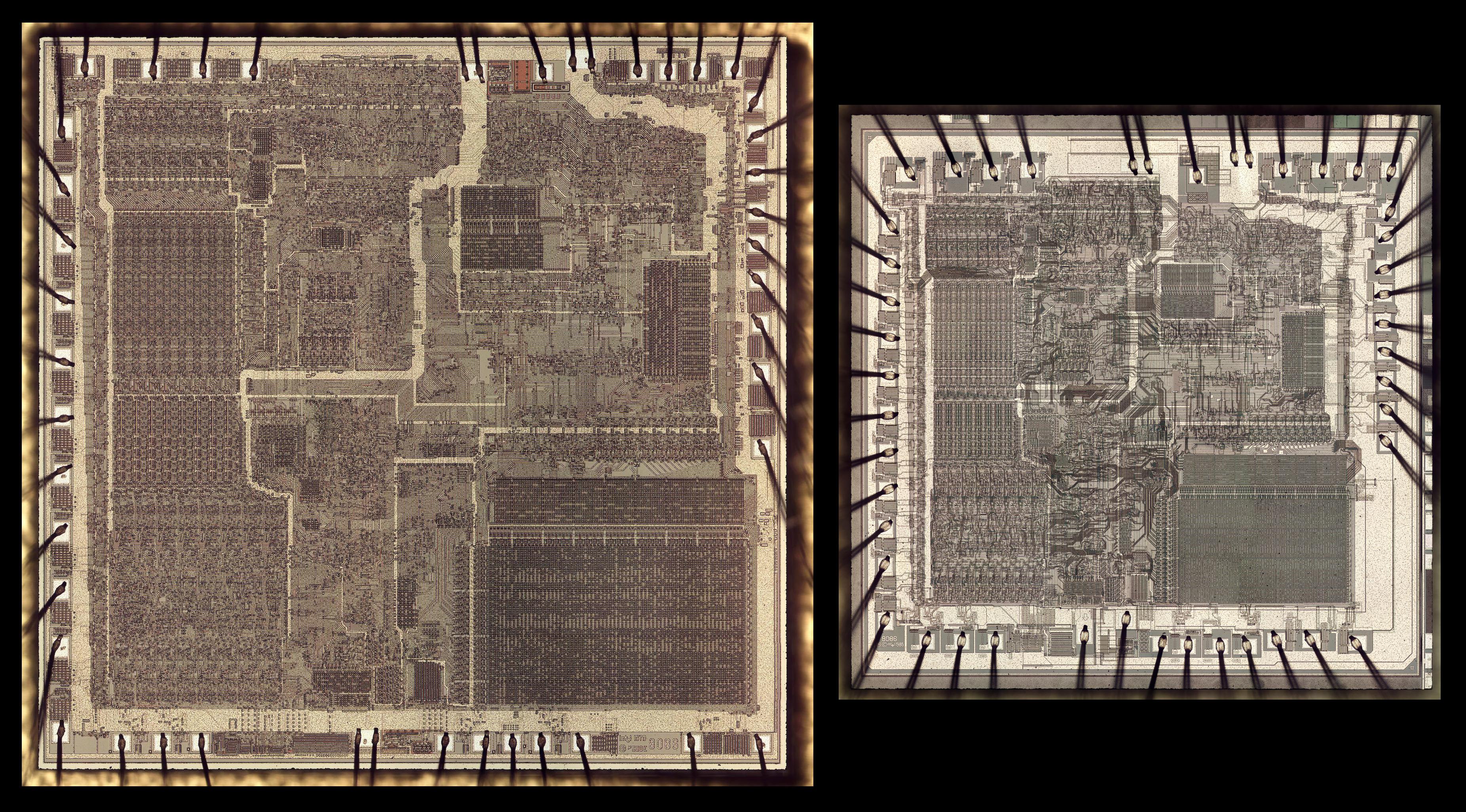

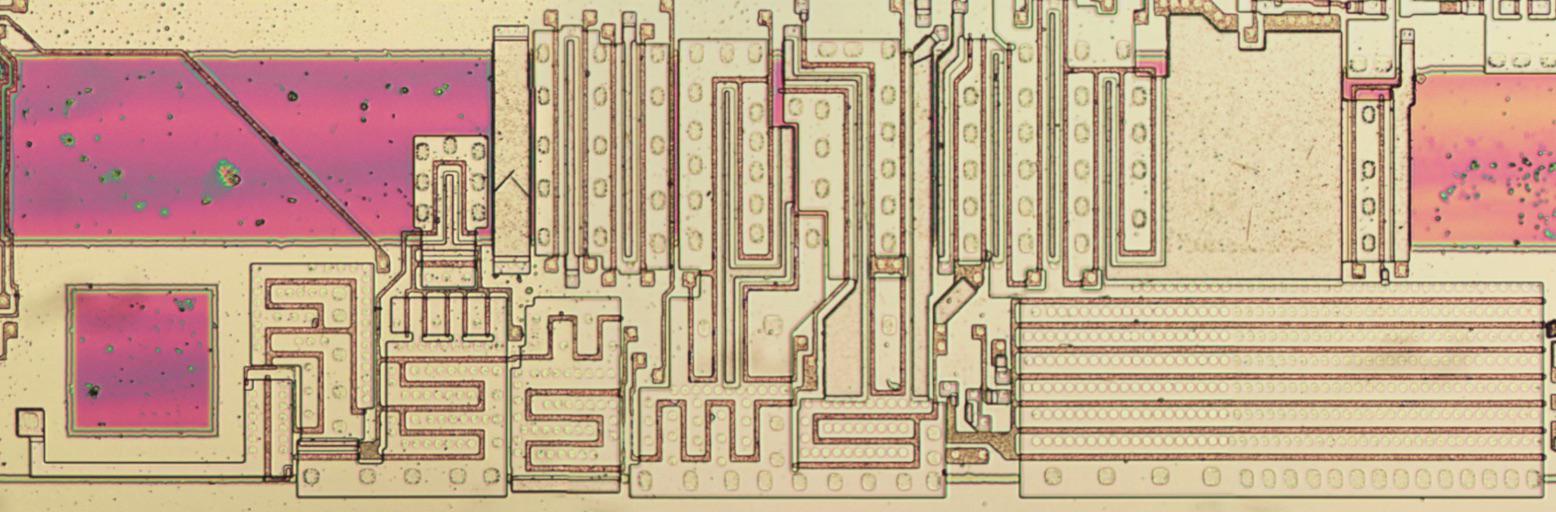

下の写真は、顕微鏡下での8086結晶を示しています。チップの上部に金属層が見え、その下にシリコン基板と導体を備えたポリポリス層が隠されています。クリスタルの周囲の外側に沿って、小さなワイヤーボンドがクリスタルのパッドを外側の脚に接続します。 8086では、電源パッドが上部にあり、接地パッドが上部と下部にあります。それぞれにワイヤーを溶接するための2本のワイヤーがあり、サポートされる電流が2倍になります。電源パッドと接地パッドから伸びる広い金属経路が見えます。それらはチップ全体に電力を分配します。

8086クリスタルの写真。電源ポイント(上)とアース接点(上と下)を見ることができます。タイミング回路は下部にあります。

8086には、同期を担当する2つの内部クロック信号があります。外部発振器は、下の入力クロックパッドを介してクロック信号を8086に供給します。内部クロックジェネレータは、外部信号に基づいて2つの高電流クロック信号を提供します。クロックドライバはチップ上で大きなフットプリントを占めることに注意してください。

この記事では、8086がチップ全体でエネルギー信号とクロック信号をリダイレクトする方法と、クロック回路が必要なクロックパルスを生成する方法について説明します。

配電

8086は3つの層で構成され、各層は導体を収容できます。金属の抵抗が低いため、上部の金属層がこれに最適です。金属の下には、特殊なタイプのシリコンからなる導体のポリペプチド層があります。ポリシリコンの抵抗は金属の抵抗よりも高いですが、それでもチップを介して信号を送信するために使用できます。トランジスタはシリコン基板上に形成されています。シリコンの抵抗は比較的高いため、たとえばゲート内など、短距離で信号を送信するためにのみ使用されます。

8086のようなチップの電力配分はトポロジカルなパズルです。金属層は抵抗が低いため、電源とアースの配線に実用的に役立つ唯一の層です。チップ上のほとんどすべてのゲートには、電源とアースを供給する必要があります。また、チップには1つの金属層があるため、電力と地面が交差することはありません。

標準のMOSゲートでは、プルダウンネットワーク用にアースが必要であり、プルアップ抵抗用に電源が必要なため、チップ上のほぼすべてのゲートに電源とアースが必要です。ただし、いくつかの例外があります。 8086は、特にALUで、速度のために動的ロジックゲートを使用します。これらのゲートは同期信号によって上方に引き付けられるため、直接電源を供給する必要はありません。 8086は、フィードスルートランジスタで複数のXORゲートも使用します。これらのゲートは、入力信号によってプルダウンされるため、アースは必要ありません。

マイクロコードROMは、電源を必要とせず、アースのみを必要とするチップの大部分を形成します。これは、ROMの各行が非常に大きなNORゲートとして実装されており、それを引き上げる電力が右端にあるためです。したがって、ROMには電源接続がないように見えますが、すべてのROMゲートには電源とアースがあります。

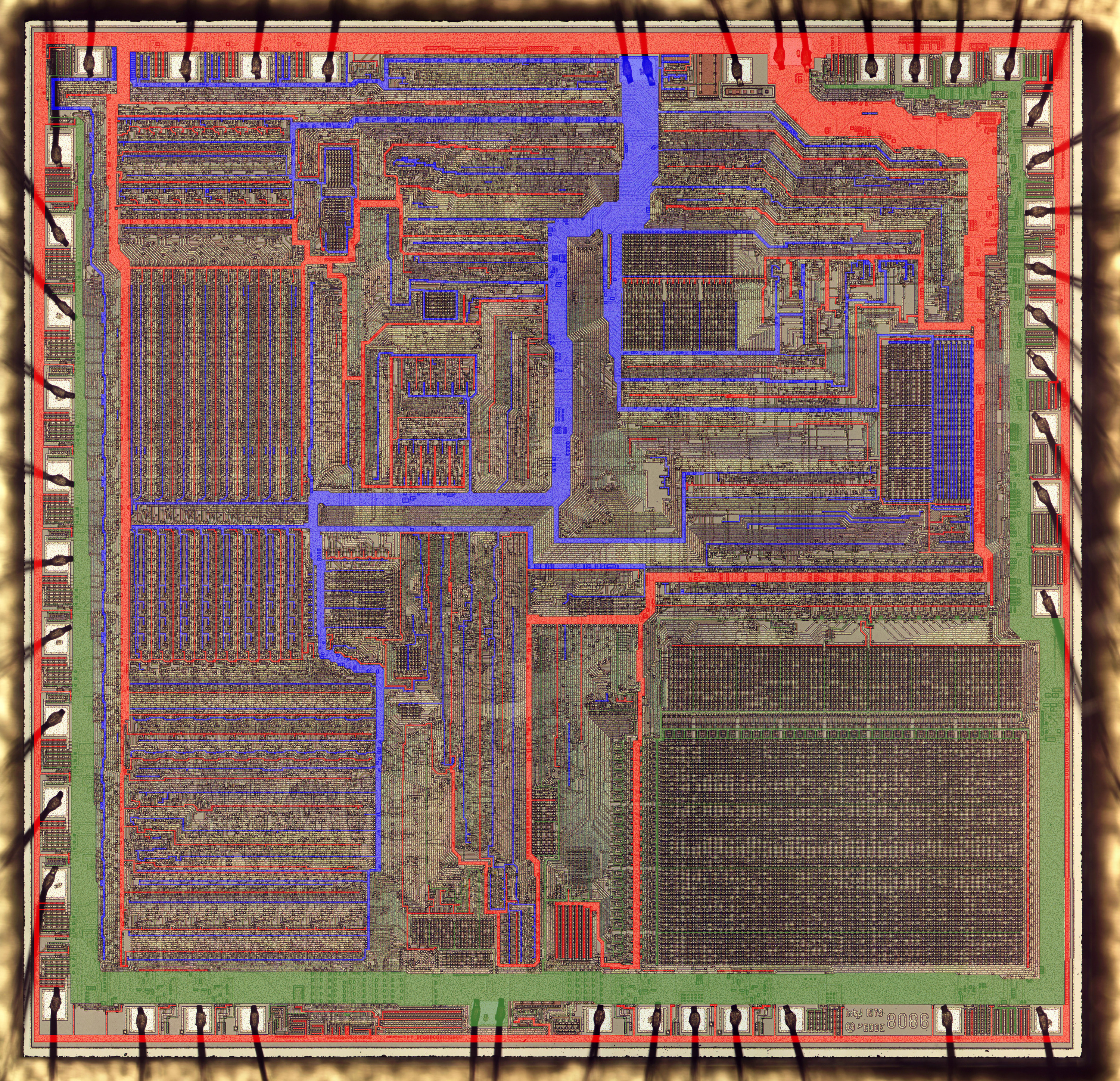

下の図は、8086の金属導体を示しています。上部の電源ピンに接続されている電源は赤で示されています。強力な食物の枝が右下に行き、それからそれは多くの枝に分かれます。電力はチップ全体のエッジに沿って流れ、I / Oピンに電力を供給します。

ICの場合、電源とアースがチップの反対側または反対側にあることがよくあります。この配置により、互いに交差しないパワートラックとグラウンドトラックのルーティングが容易になります。 8086の電源とアースは、斜めに反対側のピンにわずかに異常な位置にあり、2番目のアースは電源ピンに近い位置にあります。電力網とチップ上の土地は木のように枝分かれしています。これらのネットワークは分岐し、絡み合った指のように、チップのすべての部分に到達します。

チップの金属層の電源(赤)とアース(青、緑)

2つの接地接点があります。青でマークされたトラックは上部のアースピンに接続し、緑のトラックは下部に接続します。青いマークの付いた地面のパスは、チップの中心を通って下に分岐し、すべての方向に複雑な方法で分岐している太い分岐を示しています。緑のレーンはチップの下部、左側、右側に沿って走り、I / Oピンをサポートし、右下のマイクロコードROMに接続します。

電源から離れて端点に近づくと、電力導体が細くなり、電流が減少します。これは、以下のアドレスピンとデータピンへの電力導体で確認できます。接点の下の左側では、地面との導体は非常に広いですが、徐々に狭くなり、右側に向かっています。言い換えると、左側では、導体はすべての接点から電流を伝導する必要があり、右側では1つだけから電流を伝導する必要があります。

アドレスピンとデータピンのアースへの接続が薄くなっています(チップの左側が90°回転)

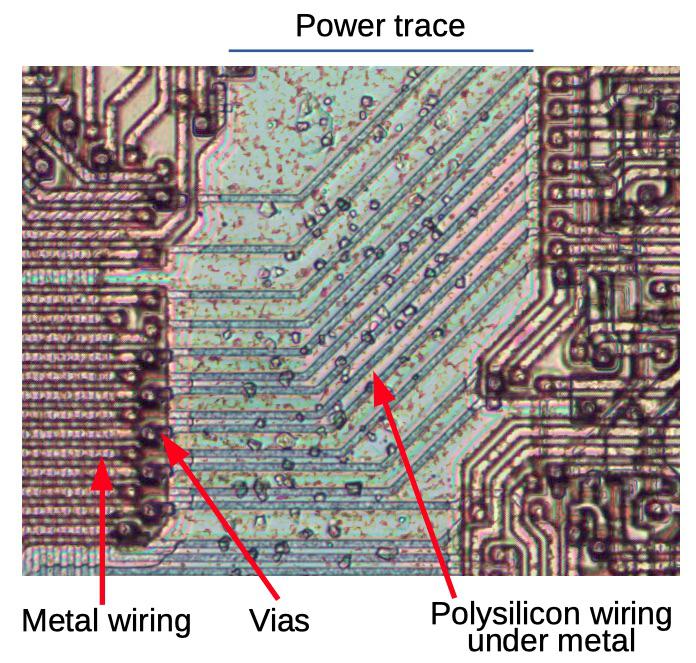

金属層は、電源とアースだけでなく、多くの信号を伝送するために使用されます。インピーダンスが低いため、最高の信号伝送層です。ただし、電力導体と接地導体が広く使用されていると、金属層の機能が制限されます。クロスオーバーを回避するために、金属層のほとんどの信号パスは電源パスと平行に走っています。その下のポリペプチドの層は、垂直信号伝送に使用されます。しかし、金属導体が電源または接地トラックを横切る必要がある場合はどうなりますか?解決策は、それを下から描くことです[クロスアンダー]。信号はポリポリスレベルまで下降し、トラックを横切ってから、以下に示すように上昇します。

このような底部交差点は、食品だけでなく、多くの場合に使用されます。しかし、ほとんどの場合、それは栄養に関するものです。通常、金属導体は一方向に信号を送信するために使用され、ポリシリコン導体は垂直方向に信号を送信するために使用されます。チップ上のさまざまな場所で、これらの方向が変化し、信号伝送の主な方向に依存します。したがって、ほとんどの場合、信号は妨げられることなく伝わります。それでも、彼らはしばしば層から層へとジャンプしなければなりません。

金属層の信号は、ポリペプチド層を介して下から供給経路を通過します

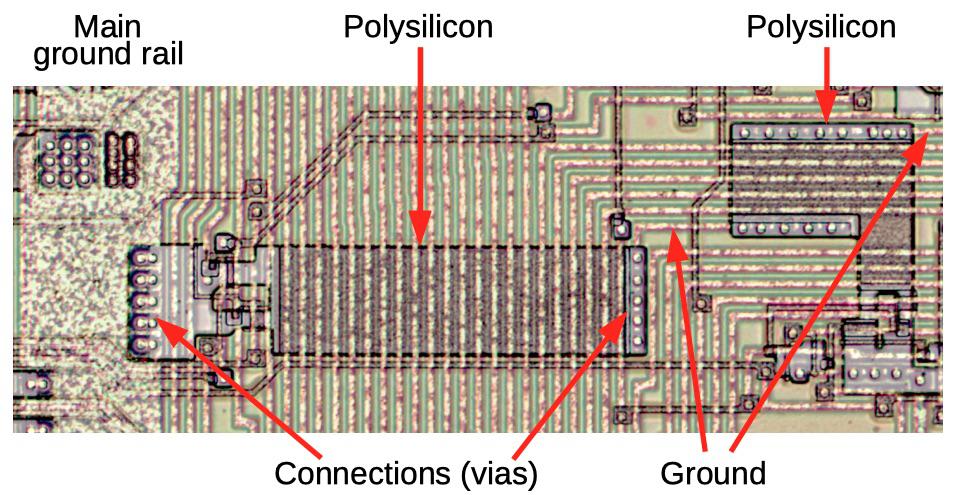

電力とアースがほぼ完全に金属層にルーティングされている場合、いくつかの場所でこの回路が壊れ、下部を通過するトラックが電力の供給に使用されます。これは、電流がすでに低いトラックの最後のセクションでより頻繁に発生します。一例を以下に示します。ここでは、ポリペプチド導体を使用して、地面が金属層の下部から2回通過します。抵抗を減らすために、これらのバイパスパスは信号パスよりもはるかに広くなり、シリコンとポリシリコンを一緒に使用します。小さな円は、金属層とポリシリコン層の間の[経由]接点を通ります。

信号経路の下のポリペプチドを通る接地バイパス経路を示す合成写真。

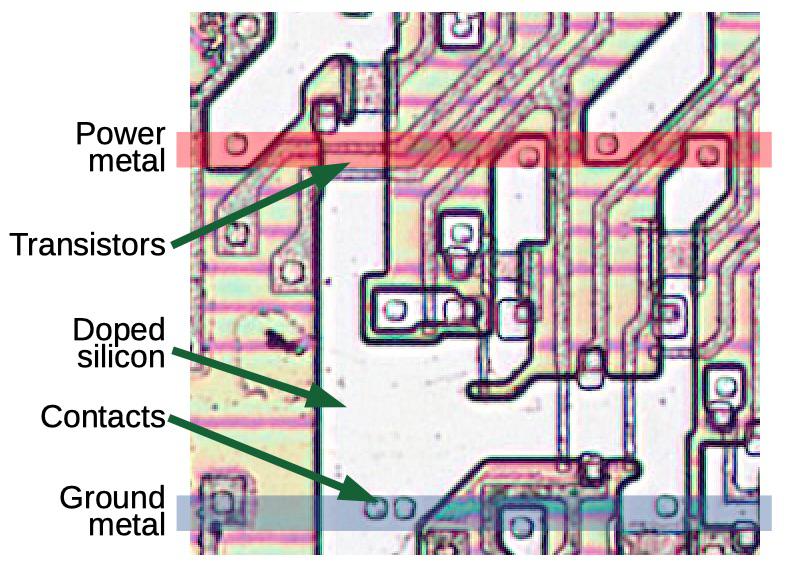

シリコン層は、電源配線で小さな役割を果たします。特に、多くのゲートは反対側から電力と地面に到達するために引き伸ばされています。下の写真は8086ゲートを示しています。地面と電源レールに到達するために引き出されたドープされたシリコン(白)の広い領域に注意してください。シリコンのごく一部だけがトランジスタに使用され、他のすべてはスペースの無駄のように見えます。ただし、シリコンのこれらの空のセクションは、ゲートを電力とアースを供給する金属導体に接続します。シリコンは比較的抵抗が大きいため、広い領域を使用し、接合部自体が短距離に伸びます。

ドープされたシリコンで作られたゲートは、電源レールと接地レールに到達するように長くすることができます。この写真では、金属層が除去されています。

8086が更新されて物理的に縮小された後、他の電源配線の問題が発生しました。製造技術の向上に伴い、Intelは結晶をスケーリングしました。回路は同じままでしたが、それに比例して減少しました。残念ながら、電源トラックのサイズを小さくすると、最大電流も減少します。この問題を解決するために、チップ周辺の電力経路が強化され、内部回路と配線が削減されました。これは下の写真で見ることができます-たとえば、小さい8086の右下隅にはさらに多くのパワートラックがあります。

同じスケールの8086の2つのバージョン。右側のクリスタルは後のバージョンで、サイズが縮小されています。

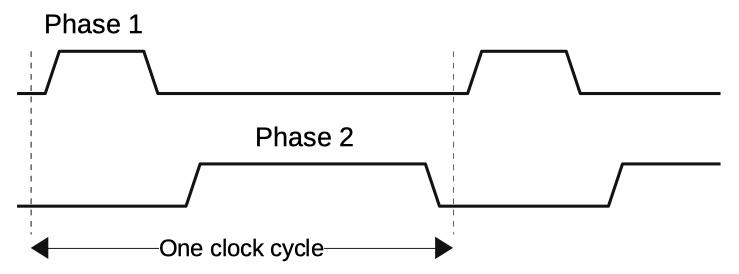

ほとんどすべてのコンピューターは、クロック信号を使用してプロセッサーのタイミングを制御します。 8086は、多くのマイクロプロセッサと同様に、内部で2相クロックドライバを使用します。以下に示すように、2相クロックドライバには2つのクロックがあります。最初のクロックがハイの場合、2番目のクロックがローの場合、またはその逆です。一部の回路は最初の同期信号でオンになり、他の回路は2番目の同期信号でオンになります。 8086の動作スキームは、同期信号の2つのフェーズとそれらの非対称性の間にオーバーラップがないことを意味します。つまり、1つの同期信号がローになり、2番目のフェーズが上昇する瞬間の間にギャップがあります。

2相クロックドライバーは、反対の極性の2つのクロック信号で構成されます

ほとんどすべてのコンピューターは同期にクロック信号を使用しますが、マシンはIASアーキテクチャ(1950年代に人気)は非同期であり、クロック信号なしで動作していました。代わりに、各回路が終了すると、次の回路にパルスを送信し、次のステップをトリガーします。 CYCLONE、ILLIAC、JOHNNIAC、MANIAC、SEAC、IBM 701など、1950年代初頭のコンピューターの多くはこのアーキテクチャに基づいていました。非同期コンピューティングの可能性に関する研究は続けられていますが、同期システムが確かに支配的です。

プロセッサは、とりわけ、回路での不要なフィードバックを防ぐためにクロック信号を使用します。たとえば、チェーンが値をインクリメントしてカウンターにフィードバックするソフトウェアカウンターについて考えてみます。新しい値が増え続けることは望ましくありません。

1つの方法は、信号がローからハイになったときに値を更新するトリガーを使用することです。その後、必要な時間だけカウンターが更新されます。ただし、2相同期信号を使用すると、レベルセンシティブラッチで回路を作成できます。その設計は、信号の変化に敏感なトリガーよりもはるかに簡単です。最初の同期信号がハイの場合、ラングの前半は入力値を受け取り、論理計算を実行します。 2番目の同期信号がハイの場合、チェーンの2番目の部分は前半からの結果を受け取り、必要なすべての計算を実行し、最初の部分はブロックされます。重要なのは、一度に更新できるのはチェーンの半分だけであり、不要なフィードバックを防ぐことです。

8086には厳格な入力クロック要件があり、3分の1の時間は高くなければなりません。通常、8086は8284チップと水晶振動子によって生成されました。チップは、着信クロック信号を3で除算して、8086に必要な33%のクロックデューティサイクルを提供しました。

最新のプロセッサでは、信号がチップのすべての部分に同時に移動する必要があるため、クロック信号のレイアウトは非常に複雑です。最新のプロセッサは、クロックパスの階層を使用し、各パスに沿った移動時間のバランスを取り、多くの場合、パスごとに個別のバッファリングを提供します。比較のために、8086のクロック信号のレイアウトは単純です。5〜10 MHzのクロック周波数は、最新のプロセッサのクロック周波数よりも数桁低いためです。これらの比較的低い周波数では、パスの長さは実際には重要ではないため、8086のクロックパルスは巻線パスをたどることができます。

8086は動的ロジックを使用していたため、最小クロック速度も2MHzでした。周波数が低いと、充電を更新する前に充電漏れが発生し、故障の原因となります。クロック信号を減速または停止することは不可能であったため、最小クロック周波数はデバッグの観点から不便でした。

8086の同期パス。緑が最初の同期、赤が2番目の同期で、逆位相です。

上の図は、8086のクロックパスを示しています。フェーズ1は緑、フェーズ2は赤です。チップの下部では、クロックドライバ回路が大きなスポットとして表示されます。そこから、同期信号がチップ全体に分岐します。ほとんどの場合、2つのクロックフェーズは並列に実行されますが、電源とグランドは反対側の分岐になります。

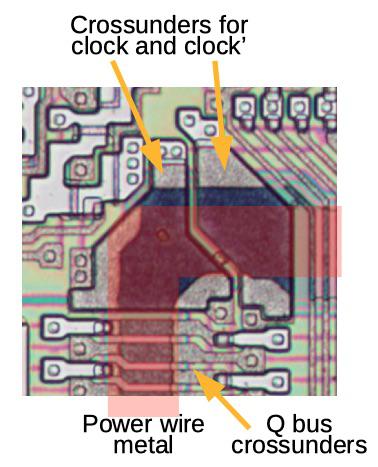

同期信号はチップのすべての部分に伝わるため、従来の信号よりもはるかに多くの電流を必要とし、そのため、ほとんどの場合、金属層に送られます。同期信号がパワートラックを通過する必要がある場合、以下に示すように、同期信号はパワートラックの下を通過します。同期の回避策は不規則な形状であることに注意してください。Qバスなどの他の信号の回避策よりもはるかに大きくなります。

電源のバイパス経路は非常に大きいです。 Qバス(コマンドキューからデコーダーにコマンドを送信する)ははるかに少ないです。

大電流同期信号を提供するために、それらのシェーパー回路は大きなトランジスタ上に構築されています。下の写真は、これらのトランジスタの1つを一般的なロジックトランジスタと比較しています。ドライバトランジスタは約300倍大きいので、約300倍の電流を供給することができます。トランジスタは、並列に配置された10個のトランジスタで構成されています。10本の垂直ポリシリコンラインが10個のゲートを形成します。各同期信号は、一方がそれを引き上げ、もう一方が引き下げる一対の大きなトランジスタによって生成されます。

隣接するロジックトランジスタと比較したクロックドライバの大きなトランジスタ

下の写真は、同期パルス発生器の概略図を示しています。この回路は、外部クロック信号を2つのフェーズに分割し、それらがオーバーラップしないようにして、それらを増幅します。左側のピンク色の四角は、外部クロックドライバー用のプラットフォームです。信号は、右側の大きなドライバートランジスタで終わる一連のトランジスタを通過します。茶色の導体は、ゲートを形成するポリペプチドです。多くのトランジスタにはジグザグゲートがあり、大きなトランジスタが小さなスペースに収まります。

オンチップクロックドライバ回路。金属層が除去されました。大きなトランジスタが見えます。外部同期入力ピン-左側のピンク色の四角。

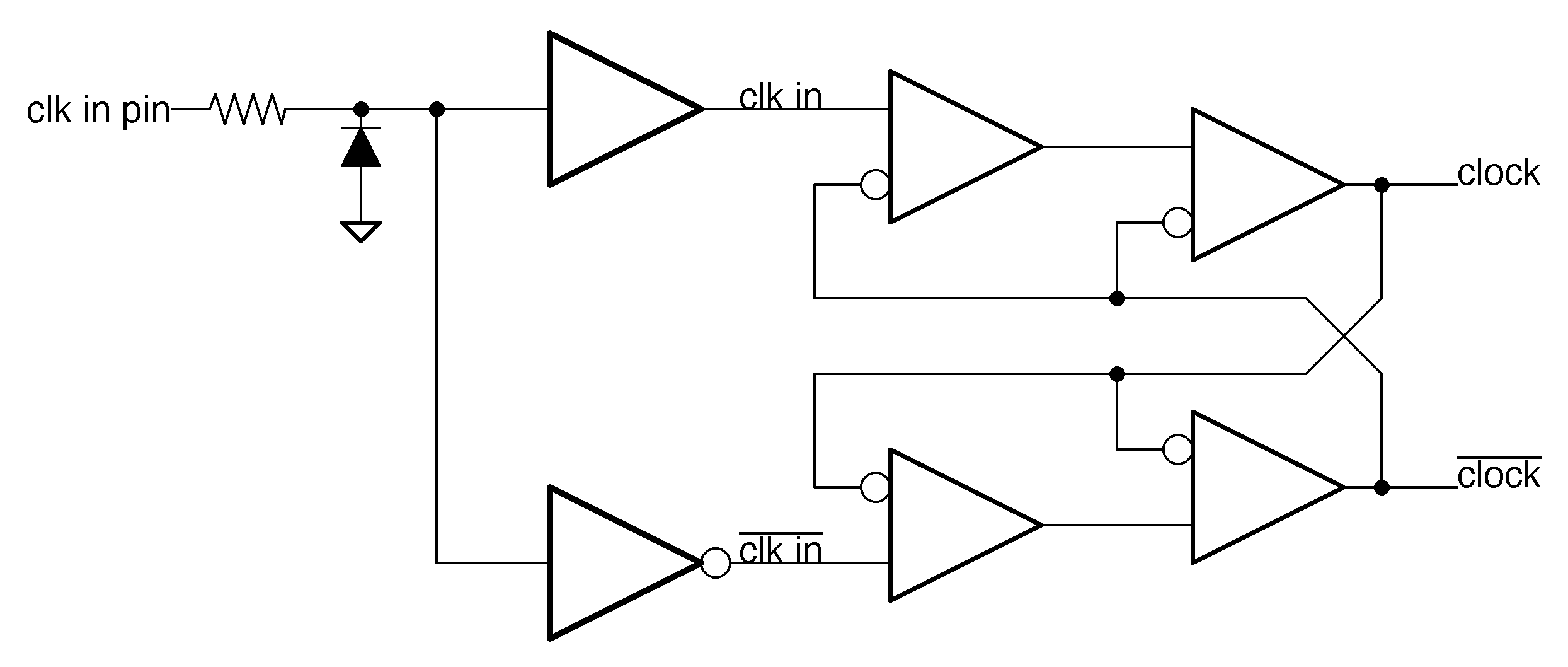

以下は、クロックジェネレータの少し簡略化された概略図です。三角形は、2つまたは3つのトランジスタで構成される大電流ドライバです。反転入力(円)は出力をプルダウンします。入力同期ピンの左側には、それを保護する小さな抵抗とダイオードがあります(他の入力ピンと同じように)。次に、同期信号は位相反転(上)と位相反転(下)に分割されます。

8086クロックジェネレータの簡略化された概略図

追加の回路は、同期信号のオーバーラップを防ぎます。1つの信号がハイの場合、これにより、反転入力を介して、2番目の信号がローになります。これがどのように機能するかを理解するために、ピンのclkの信号がハイの瞬間から始めましょう。 Clk inとclockは高く、^ clk in ^と^ clock ^は低くなっています。ここで、clk inへの着信信号がローになり、clk inへの信号が下降し、^ clk in ^が上昇するとします。ただし、^ clock ^の出力は、clockがダウンするまでアップできません。その後、信号^ clk in ^は下位のドライバーを通過し、2つのゲート遅延の後に^クロック^を引き上げます。ポイントは、クロックと^クロック^が同時に切り替わらないことです。一方がローになった後、もう一方がハイになるまでに遅延があります。その結果、重複しない同期信号を取得します。

これはかなり大まかな説明です。特に、あるトランジスタが信号をプルアップし、別のトランジスタが同じ信号をプルダウンするとどうなるかわかりません。プロセスの正確なシミュレーションは、2つのトランジスタの相対的なサイズによって異なります。

結論

8086は興味深い電力レイアウトを使用していますが、最近のプロセッサはまったく異なるレベルで動作します。 8086が350mAを必要とする場合、最新のプロセッサは100A以上を必要とする可能性があります。8086は40本の脚のうち3本を電源とアースに使用しました。最新のIntelCore i5プロセッサには、128個の電源ピンと377個のグランド(合計1151個のピンのうち)があります。最新のチップの多数の金属層は8086の配線の問題を解決しますが、チップを電源セクションに分割するなどの新しい複雑さをもたらし、未使用のセクションを無効にすることができます。

マルチギガヘルツの速度を持つ最新のプロセッサでは、トラックが1ミリ余分にあると同期信号に悪影響を与える可能性があるため、同期信号の配線ははるかに複雑になります。これらの問題を解決するために、最近のプロセッサは、8086のようにトラックを分岐するだけでなく、Hツリーやクロック分配ネットワークなどを使用します。8086には単純な2相クロック生成回路がありましたが、最近のプロセッサでは、位相ロックループを使用してクロックを合成することがよくあります。 、およびクロック信号を提供および制御するチップ全体に散在する多くの回路。しかし、8086は最新のプロセッサよりもはるかに単純ですが、興味深い回路の例が数多く含まれています。