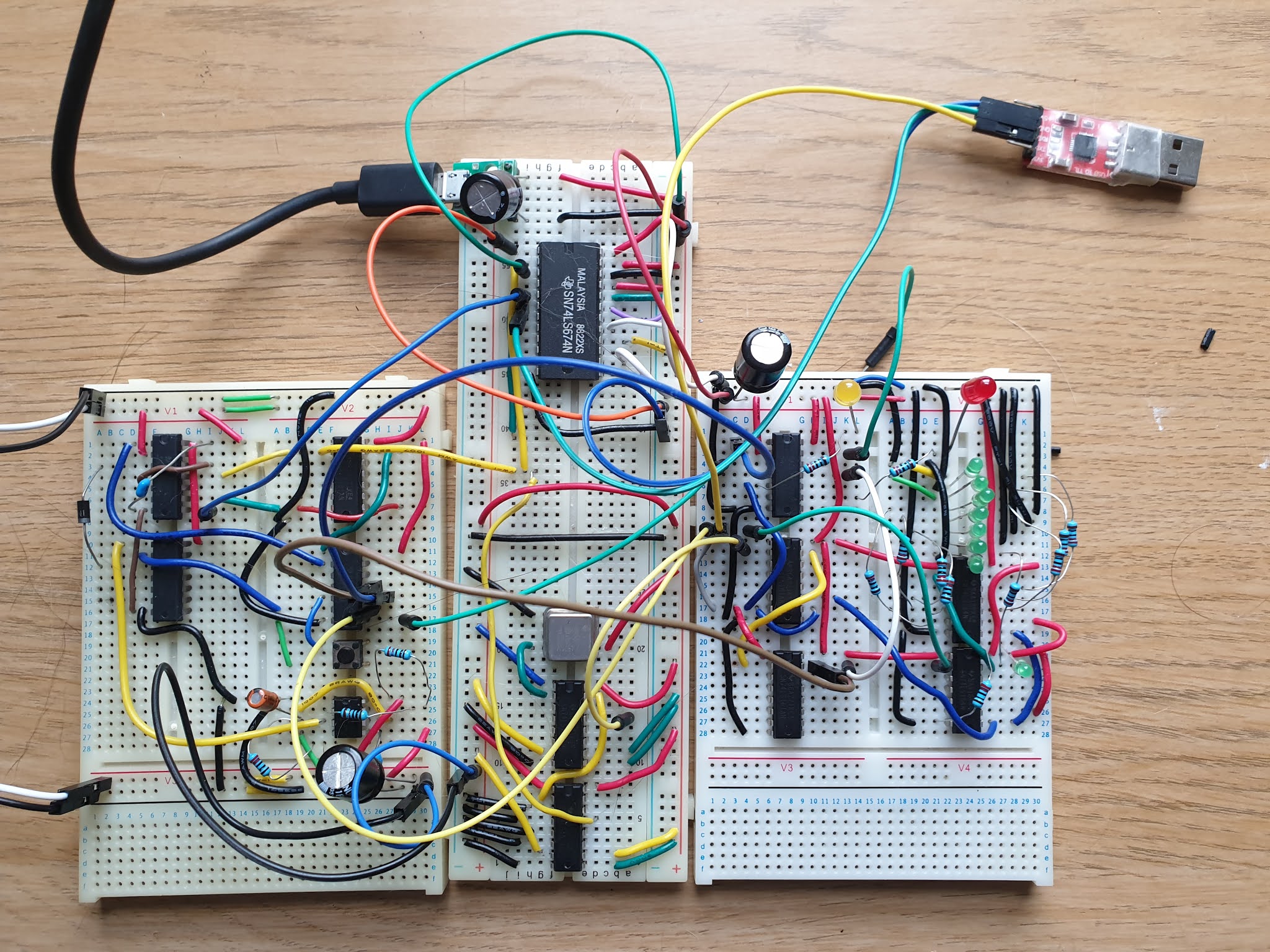

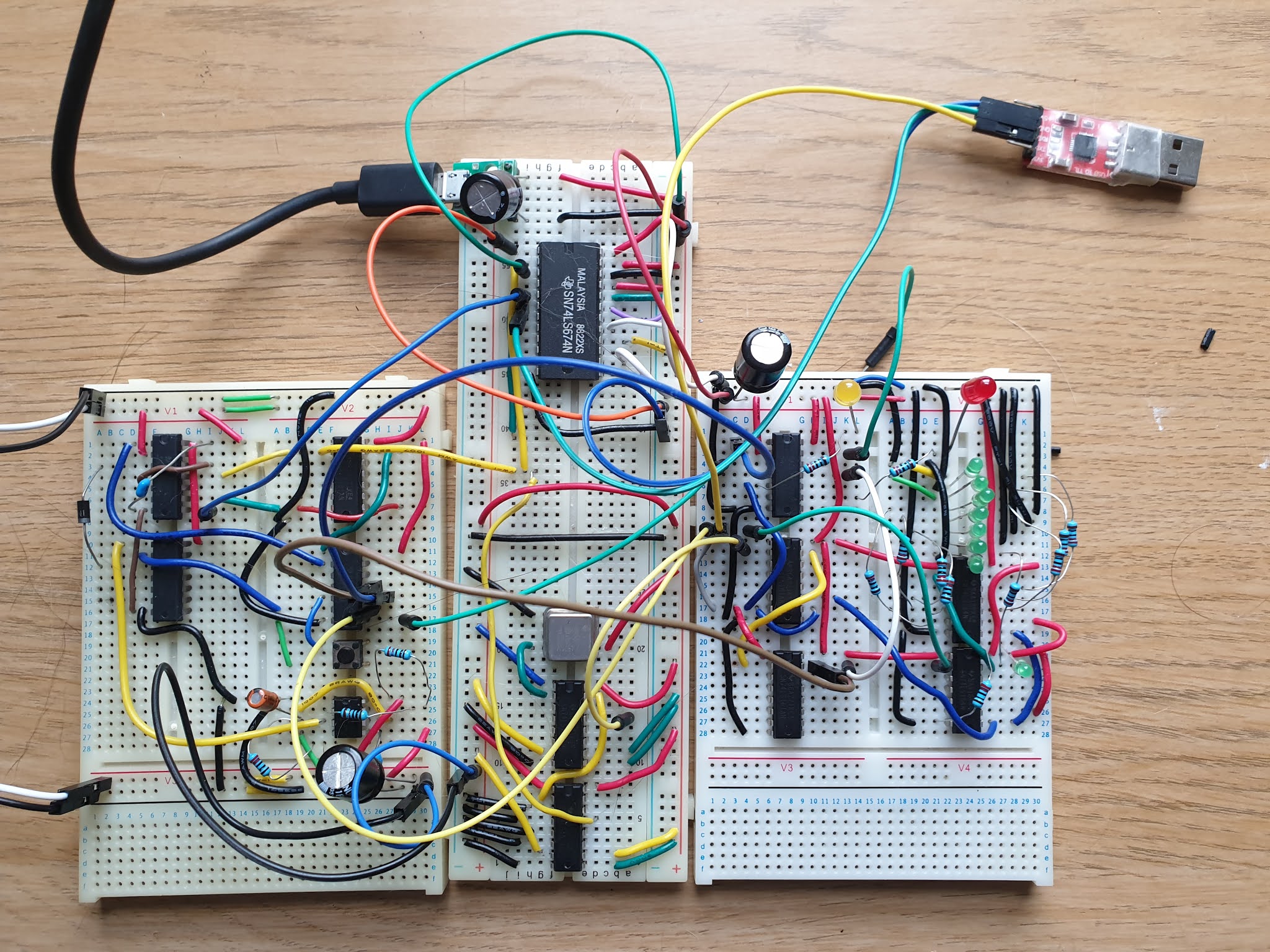

最終回路:7400シリーズICから組み立てられた完成したUARTトランシーバー

まず、UARTとは何かを理解しましょう。..。これはユニバーサル非同期トランシーバーです。これは、8ビットデータを非同期で送受信できるようにするシンプルなプロトコルであり、プロセッサーまたはコンピューターが外界と通信できるようにします。これはそれ自体で便利です。私の8ビットコンピュータはラップトップと通信し、テキストの入力と出力のインターフェイスとしてシリアルポート監視プログラム(puttyなど)を使用できます。さらに興味深いことに、8ビットコンピューター用にOSブートローダーをプログラムしてから、ラップトップからUART接続を介してプログラムすることができます。HC-05タイプのbluetoothモジュールは基本的にUARTを介してCPUと通信するため、bluetoothモジュールを使用して8ビットコンピューターを離れた場所からプログラムすることもできます。それは素晴らしいでしょう。

一部の純粋主義者は、はるかに強力なコンピューターで8ビットコンピューターをプログラミングすることを不正なアプローチと見なすでしょうが、これは私のプロジェクトであり、私のルールに従っています!プログラミングよりもデータ入力が好きで、本格的なハードワーク体験が必要な場合は、DIPスイッチを使用して手作りのマシンをプログラミングしてください。

プログラミングの場合はどうであれ、少なくともコンピューターを開発するときは、Arduino、Raspberry Pi、ESP8266、その他のTuring-completeモジュールを含まない単純なTTLチップに限定することにしました(そうでなければ、何に関心がありますか?)。

UARTプロトコルと設計上の制約

あなたの前にUART信号の構造があります。スタートビットがあり、信号のハイからローへの遷移で示され、その後にデータバイト(LSBが最初)が続き、ストップビットが信号をハイに駆動します。パリティビットもある場合もありますが、必須ではないので、簡単にするために省略しました。各ビットの送信時間は、ボーレート(この場合はビット/秒)によって決まります。たとえば、9600ボーレートは、ビットが

1/9600 =104μsで送信されることを意味します。波形は非常に単純なので、ロジックチップ上のハードウェアに完全に実装できます。

バイナリカウンターで操作すると便利なように、標準のボーレートにアクセスできる、できれば2の累乗で割り切れるクリスタルオシレーターを選択する必要がありました。少し考えた結果、2.4576 MHzの発振器を使用することにしました。これは、38400 bps(64で除算)または9600 bps(256で除算)で転送できるためです。

UART送信機

コンポーネントのリスト:

- 2.4576MHz水晶振動子

- 3 x 74LS1614ビットカウンター

- 74LS67416ビットシフトレジスタ

- 74LS06 AND

- 74LS74Dトリガー

- 74LS04ではありません

- ダイオード1N4001

- 470 uF(!)コンデンサ(パワースムージング)

スキーム

UART送信機の回路は最も理解しやすいものです。基本的にはシリアル出力のパラレルロードシフトレジスタです。データバイトをロードし、開始ビットと終了ビットを追跡し、それを目的のボーレートに同期します。次の図は、このプロセスを示しています。パート(1)では、2.4576MHzの水晶振動子が2つの4ビット74LS161カウンターを使用して38400Hzに減速されます。パート(2)では、74LS674 16ビットシフトレジスタを使用して、UARTのデータを同期します。すでに手元にあるので、このレジスターを使用します。このICは高価で見つけるのが難しいかもしれないことを理解していますが、それは間違いなく私のスキーム全体を単純化しました。

これらのICのうち3つ(2つの4ビットカウンターとシフトレジスタ)を使用すると、38,400 bps(パリティなし)で文字の連続ストリームをUART送信機に送信できます。はい、それは継続的なストリームです-シフトレジスタがロードバッファを円で更新することを考慮していませんでした-おっと。この動作は必要ありませんでした。プロセッサが一度に1バイトを送信するようにしたかったのです。プロセッサとUARTのクロックパルスが同期されていないため、事態は複雑になります。また、どちらのタイマーが速いか、どの信号がどの時点で関連するかなどについては推測したくありませんでした。非同期を確実に処理する必要があるため、次のスキームを使用することにしました。

- (3)プロセッサは、プロセッサおよびUARTクロックと同期していない「転送バイト」信号を送信します。

- «». ( AND 74LS06 D- 74LS74).

- UART «» 4- 74LS161. UART.

- (4) 16 , .

UART送信機信号の10ビットではなく16ビットをシフトしていることに注意してください。これは主に、キャリービットを使用して送信回路を無効にするのに便利なためです。10進カウンター(74LS162など)を使用することもできましたが、ブレッドボードに回路を組み立てたときに手元にありませんでした。おそらく最終的なスキームで私はそれに切り替えます。

UARTレシーバー

コンポーネントのリスト:

- 2.4576 MHzクリスタルオシレーター(レシーバーと同じオシレーターを使用できます)

- 3 x 74LS161 4ビットカウンター(レシーバーからのICの1つを使用できます)

- 74LS74Dトリガー

- 74LS04 NOT(レシーバーICを使用可能)

- ダイオード1N4001

- 470 uF(!)コンデンサ(パワースムージング)

- 美しさのための220オームの抵抗とLED。

上記のUART送信機が理解しやすい場合、受信機はやや複雑になるように思われます。ただし、デジタルロジックの優れている点は、個別のモジュールに分割できることです。そうすれば、すべてがそれほど複雑に見えなくなります。

下の図の左下隅の波形は、単一のデジタル送信機ビットを受信するときに考慮すべきことを示しています。バイトが送信されているかどうかをどのように知ることができますか?簡単-スタートビットはハイからローへの遷移で示されるので、それを反転し、ローからハイへの遷移を使用してDフリップフロップ(74LS74)を設定できます(2)。

次に、信号をシフトレジスタにシフトし、データビットシーケンスの中央でサンプリングすることにより、信号の書き込みを開始する必要があります。理解しておくべき重要なこと:UARTからデータの受信をいつ開始するかわからないため、このプロセスはクロックパルスと同期しません。したがって、インパルスが速いほど、送信機信号の真の原点に近づきます。便宜上、私のクロック速度はボーレートの16倍です(1)。これは、送信された各ビットがこのジェネレーターの16パルスを通過することを意味します。したがって、送信されたデータのほぼ中央でサンプルを取得するには、8のカウントでサンプルを取得する必要があります。このために、SAMPLING_CLK信号(3)を生成します。

次に、この新しいクロック信号の立ち上がりエッジで、送信された信号を、各データビットの中央にある2つの関連する8ビットシリアルパラレル出力シフトレジスタ(SIPO)と同期させることができます。 16番目のカウントで、最終的にデジタルビットになるため、(5)で同期されたビットの総数を追跡する別のカウンターをインクリメントします。このカウンターが16に達すると(10進カウンターである可能性があります)、Dフリップフロップをクリアすることにより、受信回路が無効になります。ふぅ!以下の図を示します。私の説明を使用して、その操作のロジックを追跡できることを願っています。

残念ながら、私はオシロスコープを持っていません。最初、私の回路はいくつかの不思議な結果を出し、1つのバイトを受け入れ、次に別の方法で別のバイトを受け入れました。 2.4576 MHzオシレーターを1秒555オシレーターに変更してカウントロジックを確認したところ、カウンターの1つのピンのフローティング入力に問題が見つかりました(LEDを使用してデバッグしていました)。両方のカウンターリセットピンをRX_active信号に接続し、カウンターをオンとリセットの間で切り替えて、各データ取得サイクルの終わりに出力をクリアしました。カウンターは期待どおりに機能するようになり、ジェネレーターを2.4576 MHzに戻すと、すべてが正しく確実に機能し始めました。

ブレッドボードの最後のコンピュータ回路には、バスへのデータ出力を制御するための出力レジスタがあります。最後に、74LS74で追加のD-flip-flopを使用してRX_READY信号を実装しました。これをプロセッサが読み取って、バイトを読み取る準備ができているかどうかを確認できます(バイトが完全に受信された場合にのみtrueになります)。

以下は、組み立てられて動作しているコンピューターの写真です。UART-USBインターフェースは、右上のドングルです。中央のボードには、さまざまなクロックパルスを生成するクリスタルオシレーターと4ビットカウンターが含まれています。上部のUSB電源の隣には、16ビットのシフトレジスタがあります。左側のボードには、1バイトの制御された送信(UART TX)のロジックが含まれています。プロセッサ制御信号をシミュレートしたボタンと、プロセッサクロックパルスとして機能する555タイマーが表示されます。UARTRXモジュールは右側のボードにあります。緑のLEDは入力へのバイトの到着を示し、黄色のLEDはデータ受信(UART RXビジー信号)を示し、赤のLEDはバイトがプロセッサによって読み取られる準備ができるとオンになります。

よりきれいなブレッドボードと配線スキルを探しています

添加

回路を少し最適化しました(途中で、ディスクリートICロジックでの非同期イベントと同期イベントの処理の違いについてのレッスンを学びました)。着信ビットをカウントし、16ビットではなく10ビットでカウントする10進カウンターを使用してチップ数を減らしたかったので、シフトレジスタを削除できました。

私は最初に74LS162カウンターを試しました。 1バイトですべてが機能しましたが、同期リセットメカニズムがあることをすぐに発見しました。つまり、信号をリセットするのに1クロックサイクルかかります。最後のビットを受信した後、クロックが停止したため、カウンターはクリアされませんでした。削除した74LS1614ビットカウンターには非同期リセットがあったため、以前はすべてが機能していました。非同期リセットの10進カウンター(74LS160)が見つかったのは良いことです。すべてが彼とうまく機能します-更新された図を参照してください。

受信したバイトのエラーをチェックする

簡単にするために、結果のバイトにエラーチェックを追加していません。パリティビットを追加し、「1」を受信するたびにフリップフロップを切り替えることを想像できます。次に、受信したビット数が偶数か奇数かがわかり、一致しない場合にフラグを設定することで、パリティビットと比較できます。さらに、これには、ストップビットが「1」に等しいことの検証チェックを含めることができます。スペースを節約するために、この機能は追加しませんでしたが、将来的に追加したいと思います。プロジェクトのモジュール性により、必要に応じてこれを行うことができます。

ノート

私はブレッドボード上の8ビットコンピューターが大好きで、このミニプロジェクトを楽しんでいました。私はかなり前からこの回路を設計してきましたが、それを組み立ててすべてが機能したとき、私はまだショックを受けました。これはある種の魔法です!ほとんど。