シリーズの以前の記事

実際、この記事は6月にDOCファイルとして登場しました。次に、5つの記事のブロックが同時に書き込まれました。ただし、DOCファイルをHabrにアップロードすることは別のタスクです。そのため、たまたまその時期が現れたのは今だけでした(そしてさらに2つが見越して苦しんでいます)。アップロードしてみると、前の記事の精神に触れないと、これはちょっとつまらないように見えることに気づきました。したがって、そのような要望がある場合は、少なくともメモリ内の最後の記事を更新するか、これら2つを更新してください(「USBバスアナライザのヘッドを作成する...」と「Quartusプロジェクトの動作をシミュレートする...」)。

前書き

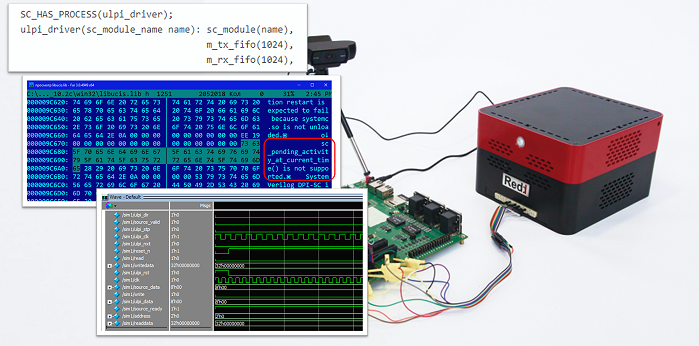

それで、完成したモデル、どこで入手できますか?私たちが開発しているアナライザーとまったく同じ問題を解決するプロジェクトがありますが、いくつかの機能があります。最初の機能は、ザイリンクスFPGA用です。第二に、それは完全に文書化されていません。なんとか動作します。既製のブレッドボードを購入して、既製のバイナリコードで埋めることもできます...そしていくつかの機能を取得します。どんな犠牲を払ってもデバイスを必要とする人は誰でも、この道をたどることができます。しかし、誰もそれを開発する方法を知りません。そのプロジェクトはここにあります。\ ulpi_wrapper \ testbenchディレクトリ内ULPIのラッパーサブシステムをテストするための一連のファイルがあります。彼らはIcarusVerilog環境でのモデリングを推奨していますが、私はうろついていましたが、SystemC言語でこれを行う方法の表面に意味のある説明は見つかりませんでした。そのため、ModelSim環境で作業を続けることにしました。それがどのように終わるかを知っていたら...しかし、私は知りませんでした。そこで、研究を始めました。プレゼンテーションの過程で、成功と失敗の両方が示されます。失敗から始めましょう。そうすれば、誰もが失敗しない方法を理解できます。

すべてを「正面から」実行しようとして失敗した

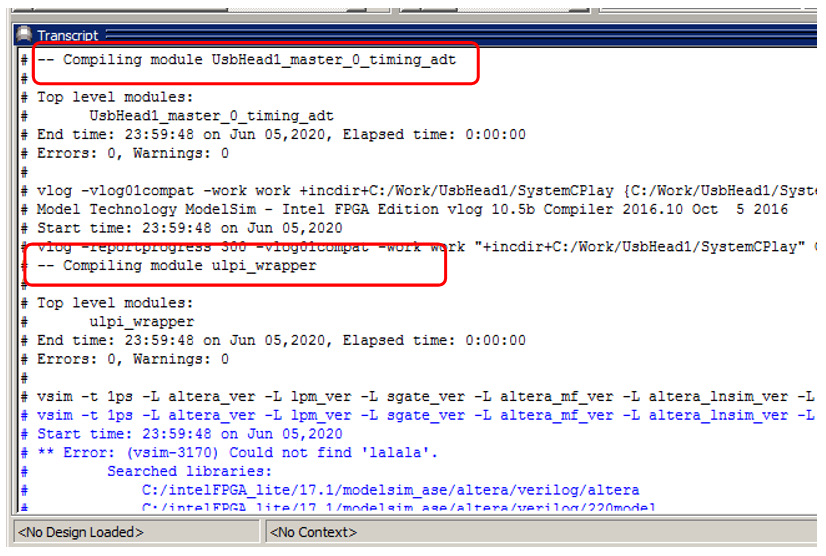

最初は、既成の例を取り上げて、モデリングを実行することにしました。通常の手の動きで(そして前回の記事で手を詰めました)、VerilogとSystemCのファイルを含むテストスイートを作成しました。

ModelSimを起動しましたが、SystemCに関連するワークグループには何も表示されません。Verilogovコードは表示されますが、Sishnyコードは表示されません。

ログを見ると、彼らがそれを収集しようとしなかったことがわかります。どうしたの?

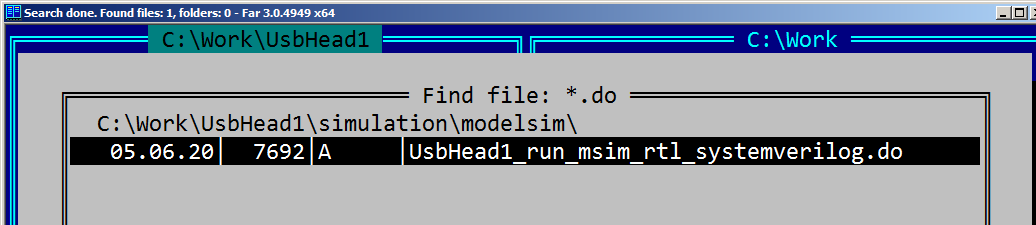

* .doファイルの構成に関する役立つ情報

* .doファイルがModelSimの実行に使用されることが知られています。しかし、「マウス」ですべてを行うのが好きなので、私は彼の中を見たことがありませんでした。それを探して開いてみましょう!プロジェクトディレクトリには、そのようなファイルは1つしかありません。これはおそらく私たちが必要としているものです。

開けます。初めに-プロジェクトに含まれるあらゆる種類のサービスアイテムとファイルのアセンブリ。

テキストを見る

transcript on

if ![file isdirectory verilog_libs] {

file mkdir verilog_libs

}

if ![file isdirectory vhdl_libs] {

file mkdir vhdl_libs

}

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

vlog -vlog01compat -work altera_ver {c:/intelfpga_lite/17.1/quartus/eda/sim_lib/altera_primitives.v}

vlib verilog_libs/lpm_ver

vmap lpm_ver ./verilog_libs/lpm_ver

vlog -vlog01compat -work lpm_ver {c:/intelfpga_lite/17.1/quartus/eda/sim_lib/220model.v}

vlib verilog_libs/sgate_ver

vmap sgate_ver ./verilog_libs/sgate_ver

vlog -vlog01compat -work sgate_ver {c:/intelfpga_lite/17.1/quartus/eda/sim_lib/sgate.v}

しかし、最後に-明らかに必要なもののアセンブリ、私はこれをulpi_wrapper.vファイルの名前で判断します:

vlog -vlog01compat -work work +incdir+C:/Work/UsbHead1/SystemCPlay {C:/Work/UsbHead1/SystemCPlay/ulpi_wrapper.v}

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -L UsbHead1 -voptargs="+acc" lalala

add wave *

view structure

view signals

run 10 us

本当に。 Verilogモジュールのアセンブリがあり、SystemCでのモジュールのアセンブリのヒントはありません。唯一の残念な点は、このDOファイルはシミュレーションを開始するたびに自動的に作成されるため、それを取得して編集することはできません。非常に複雑なTCLスクリプトによって作成されます。それを支配する欲求はありません。しかし、陽気な四半期についての記事の後、そのようなささいなことはあきらめる理由ではないことはおそらく明らかです。確かに、すべてがすでにそこにあります。唯一の残念な点は、ドキュメントに「スクリプトをこの方法で作成することも、これを実行することもできる」と記載されており、例にヒントがないことです。さて、実験的にすべてを推測しましょう。ファイルC:\ Work \ UsbHead1 \ SystemCPlay \ myrun.doを作成し、それに制御を移してみます。まず、次のようにしようとします。

メインのDOファイルは引き続き生成されますが、その末尾は次のようになります。

vlog -sv -work UsbHead1 +incdir+C:/Work/UsbHead1/UsbHead1/synthesis/submodules {C:/Work/UsbHead1/UsbHead1/synthesis/submodules/UsbHead1_master_0_b2p_adapter.sv}

vlog -sv -work UsbHead1 +incdir+C:/Work/UsbHead1/UsbHead1/synthesis/submodules {C:/Work/UsbHead1/UsbHead1/synthesis/submodules/UsbHead1_master_0_timing_adt.sv}

vlog -vlog01compat -work work +incdir+C:/Work/UsbHead1/SystemCPlay {C:/Work/UsbHead1/SystemCPlay/ulpi_wrapper.v}

vsim -t 1ps -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L cycloneive_ver -L rtl_work -L work -L UsbHead1 -voptargs="+acc" lalala

do C:/Work/UsbHead1/SystemCPlay/myrun.do

Verilogファイルがまだコンパイルされていることがわかります。その後、モデリングプロセスが開始されます(テストの実行中にこれが表示されましたが、vsimコマンドがこのプロセスを開始していることは確かです)。その後、制御が脚本。このスクリプトは、表示プロセスを制御する必要があります。しかし、それでもアセンブリを管理することはできません。収集されたファイルが十分でない場合、私たちが何かをすることを許可される前に、システムは誤って脱落します。さて、素晴らしい、最後の設定を試してみましょう。

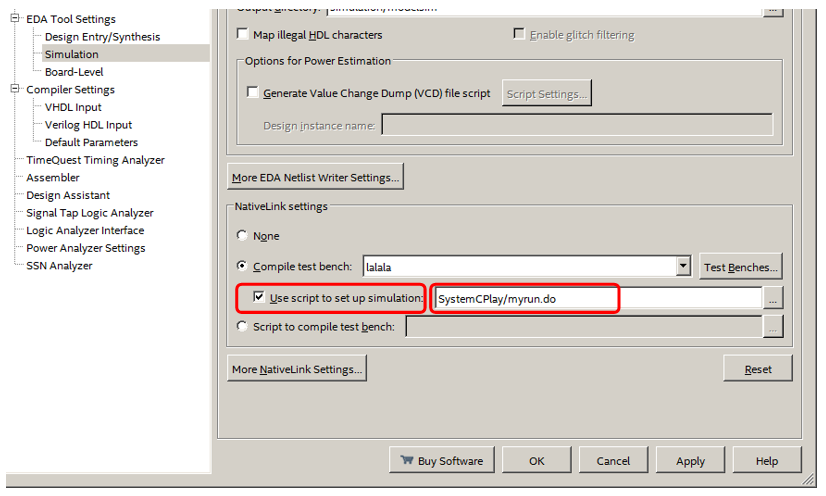

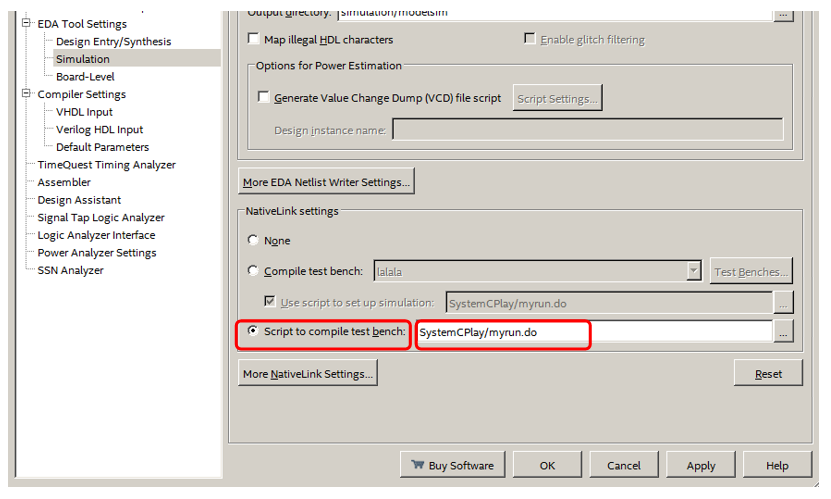

そしてここから楽しみが始まります。私がそれを組み立てるのはとても重要です。

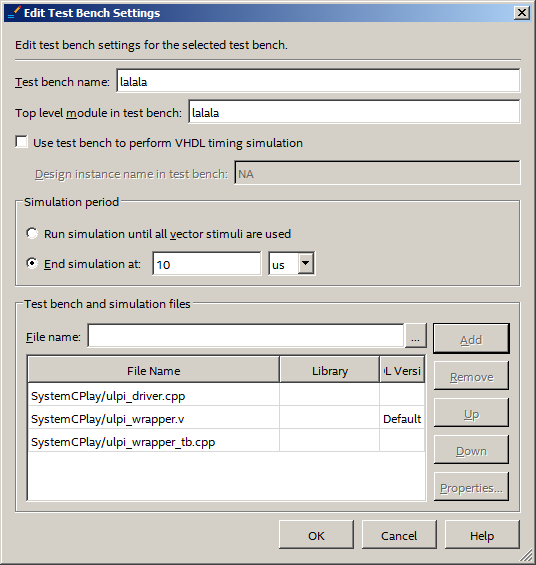

スクリプトを選択しましたが、選択されていません。設定に入ります(前に選択したオプションがあります)。私は選ぶ、選ばれない。そしてそう-顔の青にさえ。それに気付くまで、勝つ方法を見つけるまで、私は夜を殺しました!ファイルを選択するだけでは、[適用]ボタンは灰色のままであることが判明しました。そして、変更は記憶されません。他のダイアログパラメータを編集して、[適用]ボタンを黒くすることが不可欠です。上の写真では、真っ黒です。グレー表示されたままの場合、変更は保存されず、スクリプトを使用するようにすべてが再構成されることはありません。

スクリプトはまだ作成中ですが、そのエンディングは私たちにとってより便利になっています。

vlog -sv -work UsbHead1 +incdir+C:/Work/UsbHead1/UsbHead1/synthesis/submodules {C:/Work/UsbHead1/UsbHead1/synthesis/submodules/UsbHead1_master_0_timing_adt.sv}

do "C:/Work/UsbHead1/SystemCPlay/myrun.do"

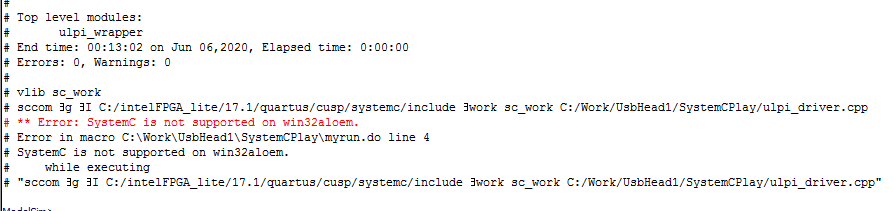

最後に、プロジェクトのソースコードを作成するプロセスは、完全に私たちの責任です。素晴らしい!当時、私はザイリンクス用に書かれたModelSimドキュメントを使用したSystemC検証しか見つけることができませんでした。しかし、ModelSimはアフリカのModelSimにあります。このドキュメントの例と過去の実験で作成されたDOファイルのサンプルを使用して、次のスクリプトテキストを作成しました(キーの数に驚かないでください。以下ではほとんどすべてを破棄し、次に絶対パスを相対パスに置き換えます。この段階では、例からすべてを引き出しました。および自動生成されたサンプル)。

vlog -vlog01compat -work work +incdir+C:/Work/UsbHead1/SystemCPlay {C:/Work/UsbHead1/SystemCPlay/ulpi_wrapper.v}

vlib sc_work

sccom –g –I C:/intelFPGA_lite/17.1/quartus/cusp/systemc/include –work sc_work C:/Work/UsbHead1/SystemCPlay/ulpi_driver.cpp

ドラムロール...そしてModelSimは私たちに宣言します:私たちが

すべての卑劣な言葉を省略した場合、私は何も言うことはありません...しかし、そのような道は渡されました!そして、どこで別のULPIモデルを入手できますか?もちろん、FPGAの本格的なプロジェクトに専門的に携わっている外国人の友人にも同意しました。特に私にとって、彼らは週末にライセンスされたModelSimを備えたマシンへのリモートアクセスを開始しました。2番目のパンケーキもゴツゴツしていることが判明しました。64ビットバージョンは、ライセンスされた形式であっても、SystemCでは機能しません。しかし、結局、ライセンスされたModelSimの32ビットバージョンで遊ぶことができました。したがって、私たちは物語を続けます...

ドキュメントについての一言

そう。ライセンスされたソフトウェアにアクセスできるようになったので、情報を探す場所とインスピレーションを得る場所について話し合うときが来ました。ウェブ上では、言語に関する情報はかなり大雑把です。ただし、システムの配信には、次の便利なディレクトリがあります

。C:\ modeltech_10.2c \ docs \ pdfdocs -PDF形式のファイルを含むドキュメント。私はファイルmodelsim_se_ref.pdf(ModelSim SEコマンドリファレンスマニュアル)、modelsim_se_user.pdf(ModelSim SEユーザーズマニュアル)、およびmodelsim_se_tut.pdf(ModelSim SEチュートリアル)が好きでした。言語自体についてはあまりありませんが、ファイルを接続する方法と方言の問題を解決する方法についてはかなりです。

次に、便利なディレクトリC:\ modeltech_10.2c \ examples..。既製の* .doファイルと既製のcppおよびhファイルの例があります。私たちにとって最も有用な例はCです:\ modeltech_10.2c \ examples \ systemc \ vlog_sc。VerilogコードからSystemCコードにアクセスする方法を示します。最終的には、まさにこのようになります。C:\ modeltech_10.2c \ \ SystemCのディレクトリを含めるには、言語のタイプライブラリのソースコードが含まれています。悪いリファレンスブックではありません。彼らが言うように、魚のいないことと癌のための魚がいます。 カタログからすべて。今、あなたは言語とその中のプログラミング技術の両方について多くを学ぶことができる素晴らしい本のタイトルです。SystemC-ゼロから、第2版。David C. Black、Jack Donovan、Bill Bunton、AnnaKeistによる。

SystemCダイアレクト

そう。以前に作成したスクリプトに従って、作業システムにアクセスできるようになり、プロジェクトを楽しく組み立てました。彼は間違いなく組み立てました!GitHubの最初のモデルは、私たちと協力することに同意しました。ベンチマークを実行したいので、同じディレクトリからulpi_wrapper_tb.cppファイルをプロジェクトに追加したところ、大量のエラーが発生しました。次の行にエラーがあるとします

。m_vpi_handle= vpi_handle_by_name((const char *)name、NULL);

修正するのは難しいですが、それでも可能です。しかし、ライン

// Update systemC TB

if(sc_pending_activity())

sc_start((int)(time_value-m_last_time),SC_NS);

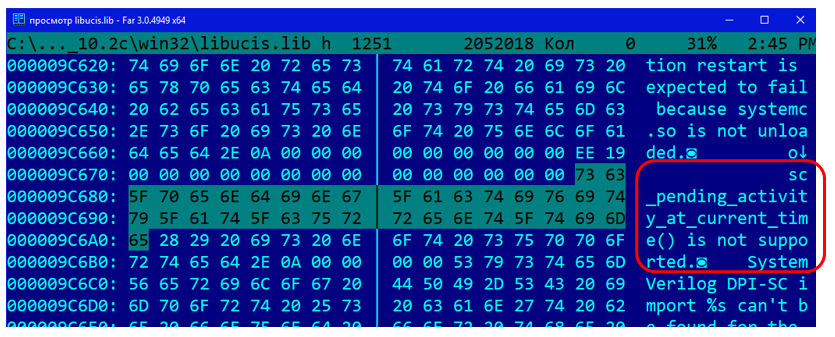

悪い考えを思い起こさせた。ライブラリにはsc_pending_activity()関数はありません。sc_pending_activity_at_current_time()関数がありますが、私はそれを処理することさえしませんでした。千の説明の代わりに、私はダンプを与え

ます:そしてこのテキスト(* .exe、* .dllなど)を含む44のファイルがありました。

あなたはすべてを書き直そうとすることができます...しかし、それは必要ですか?準備ができているものをすべて使いたかったので、実際にこれをすべて始めたことを思い出させてください。本当に多くの時間を無駄にすれば、純粋なSystemVerilogで無料の環境ですべてを開発できます...時間を無駄にするのではなく、節約するためにここに行きました!しかし実際には...主なことは私たちがしていることを忘れないことです。ULPIバスモデルを使用したいと思います。彼女は集まった。例から完全なテストシステムを構築しようとすると問題が発生しました...これはなぜですか?まあ、完全なシステムは機能しません、そして大丈夫です。システムの動作を見ずに、試行錯誤しながら1つのモデルをマスターします。

方言に基づく誤解を排除する

そう。混合システムを実行します。モデルを含むモジュールはSystemC言語で記述され、テストアクションとVerilog言語で開発されているモジュールを送信します。つまり、ulpi_driverモジュールをワークグループに表示する必要があります。

ModelSimの配信からのサンプル* .doファイルを調べて、スクリプトを大幅に簡略化し、最終的に次のようにしました。

vlog +../../SystemCPlay {../../MyCores/ULPIhead.sv}

sccom -g ../../SystemCPlay/ulpi_driver.cpp

sccom -link

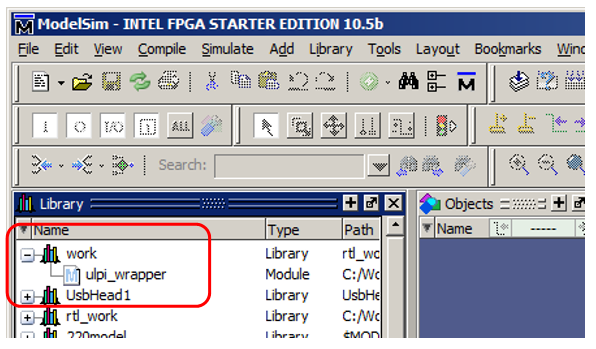

エラーはありませんが、モジュールもグループに表示されませんでした。サンプルファイルを調べて(この言語の混合を正確に実装する最良の例はC:\ modeltech_10.2c \ examples \ systemc \ vlog_scディレクトリにあることを思い出してください)、ulpi_driver.cppファイルの最後に次の行を追加する必要があることに気付きました:

SC_MODULE_EXPORT(ulpi_driver);

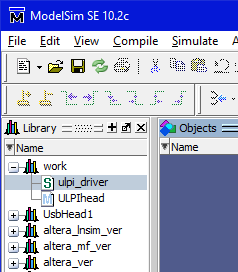

ModelSimのドキュメントには、これらは方言機能であると記載されています。そして出来上がり!これがモジュールです

。True、Create Waveメニュー(前回の記事でこのメニューについて説明しました)は使用できません。そして、彼にはポートがありません。歴史的に、私は最初にポートを扱いましたが、系統的に-ポートについての話は後で延期します。それ以外の場合は、コードを2回編集する必要があります。これを避けるために、最初に少し準備をしましょう。

クロックジェネレーターの作成

モデルには実際のULPIとはいくつかの違いがあることが判明しました。最初の違いは、66MHzのクロックをチップで生成する必要があることです。モデルには何が表示されますか?

sc_in<bool> clk_i;

障害!リワークを始めましょう!特に明記されていない限り、すべての作業はulpi_driver.hファイルで実行されます。

ポートタイプを変更します。そうだった:

sc_in<bool> clk_i;

になりました(ポート名も変更しました):

sc_inout<bool> clk;

私は本から、変数を追加することによって実際のジェネレーターが挿入されることを学びました。

sc_clock oscillator;

コンストラクターでパラメーターを設定します。その結果、コンストラクターは次の形式になります。

//-------------------------------------------------------------

// Constructor

//-------------------------------------------------------------

SC_HAS_PROCESS(ulpi_driver);

ulpi_driver(sc_module_name name): sc_module(name),

m_tx_fifo(1024),

m_rx_fifo(1024),

oscillator ("clk66",sc_time(15,SC_NS))

{

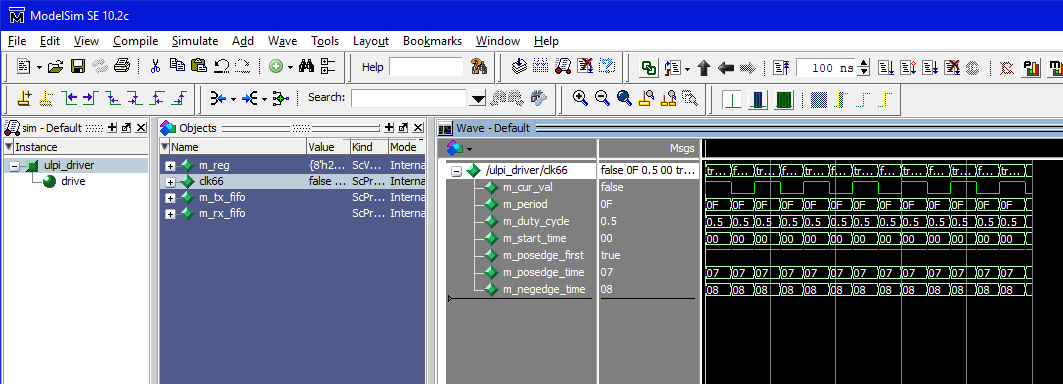

最後の行はこれだけです。必要に応じて、シミュレーションを開始し、usb_driverモジュールをダブルクリックしてから、clk66を一時的な小屋に引っ張って、シミュレーションプロセスを少し実行することもできます。ジェネレータがどのように機能するかはすでに見てきました

。メインスレッドが開始する場所でクロック信号の名前を変更することを忘れないでください。そうだった:

SC_CTHREAD(drive, clk_i.pos());

なりました:

SC_CTHREAD(drive, clk.pos());

内部リンクは置き換えられました。しかし、信号を外に出すことがどれほど美しいか、私は見つけませんでした。おそらく私は資格が不足しています。しかし、どういうわけか、ポートを引き出すすべての試みは失敗しました。いつも何かが邪魔でした。あるフォーラムで、著者が同じことをする必要があるディスカッションを見つけました。チームは、入力ポートにのみ転送できると判断しました。しかし、私たちは出て行く必要があります!したがって、これを行います。

コンストラクターの下にストリーム関数を追加します。

void clkThread(void)

{

while (true)

{

wait(oscillator.posedge_event());

clk.write (true);

wait(oscillator.negedge_event());

clk.write (false);

}

}

そして、クラスコンストラクターにリンクを追加します。

SC_THREAD(clkThread);

現在の結果の全体像を示すために、現在のコンストラクター領域を示します。

SC_HAS_PROCESS(ulpi_driver);

ulpi_driver(sc_module_name name): sc_module(name),

m_tx_fifo(1024),

m_rx_fifo(1024),

oscillator ("clk66",sc_time(15,SC_NS))

{

SC_CTHREAD(drive,clk.pos());

SC_THREAD(clkThread);

m_reg[ULPI_REG_VIDL] = 0x24;

m_reg[ULPI_REG_VIDH] = 0x04;

m_reg[ULPI_REG_PIDL] = 0x04;

m_reg[ULPI_REG_PIDH] = 0x00;

m_reg[ULPI_REG_FUNC] = 0x41;

m_reg[ULPI_REG_OTG] = 0x06;

m_reg[ULPI_REG_SCRATCH] = 0x00;

}

void clkThread(void)

{

while (true)

{

wait(oscillator.posedge_event());

clk.write (true);

wait(oscillator.negedge_event());

clk.write (false);

}

}

すべて。最初の編集が完了しました。

双方向データバスの作成

ULPIには双方向データバスがあります。そして、モデルには次の説明があります。

sc_out <sc_uint<8> > ulpi_data_o;

sc_in <sc_uint<8> > ulpi_data_i;

障害!最初に出力バスに基づいてブランクを作成し、次にすべてをそれに切り替えます。どこから始めますか?バスは3番目の状態に入ることができなければならず、sc_uint <8>タイプはバイナリデータでのみ機能するという事実から。sc_lv <8>タイプが役に立ちます。したがって、タイヤ宣言を次のように変更します。

sc_inout <sc_lv<8> > ulpi_data_o;

次に、ulpi_driver.cppファイルに移動し、そこでulpi_data_oバスへのすべての呼び出しを探します。直感的に、修正する場所は1つしかないことに気付きました。

同じテキスト。

void ulpi_driver::drive_input(void)

{

// Turnaround

ulpi_dir_o.write(false);

ulpi_nxt_o.write(false);

ulpi_data_o.write(0x00);

wait(oscillator.posedge_event());

}

選択した行をに変更します

ulpi_data_o.write("ZZZZZZZZ");

すべて。これで、2行の代わりに次のことができます。

sc_inout <sc_lv<8> > ulpi_data_o;

sc_in <sc_uint<8> > ulpi_data_i;

1つ書く:

sc_inout <sc_lv<8> > ulpi_data;

そして、h-nickとcpp-shnikの両方の古い変数へのすべての参照をulpi_data変数への参照に置き換えます。

ポートエイリアスを追加する

そう。長い検索の結果、ModelSim環境では、GUIを使用してSystemCの別のモジュールのポートを簡単に取得して確認できるという結論に達しました(おそらく誤りです)。ただし、このモジュールをテストシステムに挿入すると、表示されます。しかし、理論を調べているうちに、ポート名のエイリアスを美しく設定する方法を見つけました。最終的なクラスコンストラクタは次のようになります。

SC_HAS_PROCESS(ulpi_driver);

ulpi_driver(sc_module_name name): sc_module(name),

m_tx_fifo(1024),

m_rx_fifo(1024),

oscillator ("clk66",sc_time(15,SC_NS)),

rst_i ("rst"),

ulpi_data ("data"),

ulpi_dir_o ("dir"),

ulpi_nxt_o ("nxt"),

ulpi_stp_i ("stp")

{

SC_CTHREAD(drive,clk.pos());

SC_THREAD(clkThread);

m_reg[ULPI_REG_VIDL] = 0x24;

m_reg[ULPI_REG_VIDH] = 0x04;

m_reg[ULPI_REG_PIDL] = 0x04;

m_reg[ULPI_REG_PIDH] = 0x00;

m_reg[ULPI_REG_FUNC] = 0x41;

m_reg[ULPI_REG_OTG] = 0x06;

m_reg[ULPI_REG_SCRATCH] = 0x00;

}

テストシステムの作成

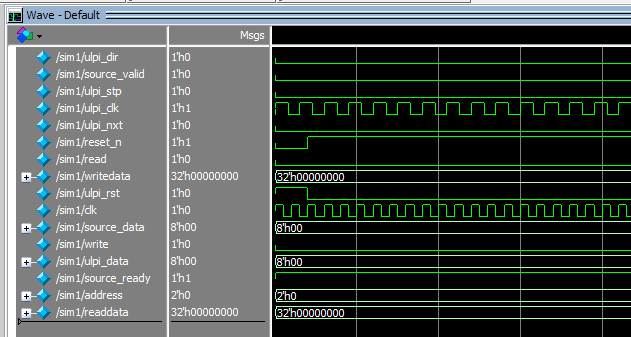

じゃあ。 2つのデバッグされたモジュール(アナライザーヘッドとULPIバスモデル)がテストファイル自体にジャンプするように、すべてを自動的に実行することに成功しませんでした。しかし、少なくともヘッドテストを行い、それにULPIを追加しましょう。前回の記事の手法を使用して、ULPIhead.svファイルのテストシステムを作成しました。sim1.vというファイルがあり、すぐにsim1.svという名前に変更しました。

次に、ハンドル付きのulpi_driverモジュールを追加しました。結果のスクリプトmyrun.doは次のようになります。

vlog +../../SystemCPlay {../../MyCores/ULPIhead.sv}

sccom -g ../../SystemCPlay/ulpi_driver.cpp

sccom -link

vlog +../../SystemCPlay {../../SystemCPlay/sim1.sv}

vsim -voptargs="+acc" sim1

最後の行は拷問されています。それがなければ、Verilogコードにはポートがありませんでした。最適化パラメータを変更することで、この問題を解消します。私はそれを、すべてがまだマシン上で行われていた最初の段階でシステムをシミュレートするために作成された* .doファイルで見ました。確かに、長い列があります。問題を解決する鍵を見つけてコピーしました。だから-私は長い列が好きではありません、私は不要なものをすべて捨てました。

次に、ULPIブロックをテストシステムに追加し、ダミーテストを作成します。すべてのクロック信号がカチカチ音をたてており、バスが正しい値に設定されていることを確認するためです。

私はこのテストを受けました。

テキストを見てください。

`timescale 1ns / 1ns

module sim1 ;

reg ulpi_dir ;

wire source_valid ;

wire ulpi_stp ;

reg ulpi_clk ;

reg ulpi_nxt ;

reg reset_n ;

reg read ;

reg [31:0] writedata ;

wire ulpi_rst ;

reg clk ;

wire [7:0] source_data ;

reg write ;

wire [7:0] ulpi_data ;

reg source_ready ;

reg [1:0] address ;

wire [31:0] readdata ;

always

begin

clk = 1;

#5;

clk = 0;

#5;

end

ULPIhead DUT

(

.ulpi_dir (ulpi_dir ) ,

.source_valid (source_valid ) ,

.ulpi_stp (ulpi_stp ) ,

.ulpi_clk (ulpi_clk ) ,

.ulpi_nxt (ulpi_nxt ) ,

.reset_n (reset_n ) ,

.read (read ) ,

.writedata (writedata ) ,

.ulpi_rst (ulpi_rst ) ,

.clk (clk ) ,

.source_data (source_data ) ,

.write (write ) ,

.ulpi_data (ulpi_data ) ,

.source_ready (source_ready ) ,

.address (address ) ,

.readdata (readdata ) );

ulpi_driver ULPI

(

.clk (ulpi_clk),

.rst (ulpi_rst),

.data (ulpi_data),

.dir (ulpi_dir),

.nxt (ulpi_nxt),

.stp (ulpi_stp)

);

initial

begin

reset_n = 1'b0;

source_ready = 1;

writedata = 0;

address = 0;

read = 0;

write = 0;

#20

reset_n = 1'b1;

end

endmodule

結論

少なくとも、ModelSimシステムを使用してSystemC言語でモデリングを習得しました。ただし、このためには、ライセンスされた32ビットバージョンにアクセスする必要があることが判明しました。無料版とライセンスされた64ビット版はそのような機会を提供しません。私が理解しているように、Icarus Verilogシステムではすべてが完全に無料で実行できますが、これを実現する方法を正確に理解していませんでした。必要なModelSimにアクセスする方が簡単であることがわかりました。次の記事では、この知識を使用して頭をモデル化します。

作業の過程で、モデルの非常に複雑な変更が行われました。結果のファイルはここからダウンロードできます。