1 1974年、Hewlett-Packardは、フロッピーディスクドライブから電圧計まで、製品のさまざまな機能を制御するマイクロプロセッサを開発しました。この単純なプロセッサは、標準のマイクロプロセッサに対応していませんでした。加算や減算もサポートしていなかったため、「ナノプロセッサ」と呼ばれていました。 Nanoprocessorの主な機能は、低コストと高速作業でした。最新のMotorola 6800の価格は360ドル、Nanoprocessorのコストは15ドルで、制御操作ははるかに高速でした。

追加操作はありませんでしたが、Nanoprocessorは(サポートされている操作)を繰り返しインクリメントまたはデクリメントすることで(ゆっくりと)数値を追加できました。他のケースでは、たとえば、Hewlett-Packardの電圧計を使用して、ALUチップ(74LS181)が製品に追加され、迅速な追加が行われ、I / Oデバイスとしてアクセスされました。当然、Turingが完成しているため、Nanoprocessorは理論的には、浮動小数点関数の計算からCrysisゲームの起動まですべてを実行できます。それは非常に遅いでしょう。

プロセッサの写真テンプレートは、リンク(122 MB PSD)からダウンロードできます。

HP Nanoprocessor, 1820-1691. , -2,5 , – . , .

その後の数十年間、プロセッサは最近までその開発者であるラリーバウアーがCPUシャックとチップのフォトマスクとドキュメントを共有するまで不明のままでした。そこで彼らはフォトマスクをスキャンし、ナノプロセッサーについての記事を書きました。Antoine Berkovichiが画像を1つにつなぎ合わせた後、それに基づいてNanoprocessorのレビューを書きました。これは記事の第2部で、フォトマスクに基づいてリバースエンジニアリングを行うナノプロセッサ回路の詳細について説明します。ナノプロセッサの機能ブロックは、有用なマイクロプロセッサを維持しながら、必要な機能の最小限の実装をバイパスするため、研究するのに興味深いものです。

ナノプロセッサーの内部

その時代のほとんどのプロセッサと同様に、ナノプロセッサは8ビットです。ただし、ランダムアクセスメモリはサポートされておらず、コードは外部2KBROMから実行されます。 16個の8ビットレジスタがあります。これはほとんどのプロセッサよりも多く、多くのアプリケーションのメモリ不足を補うのに十分です。ナノプロセッサには48の命令があり、Motorola 6800の72の命令よりも大幅に少ないです。ただし、ナノプロセッサには、当時の他のプロセッサにはなかった便利なビットセット、クリア、およびチェック操作のセットがありました。また、I / Oポートと汎用I / Oピンの両方をサポートするいくつかのI / Oコマンドがあり、他のデバイスを簡単に制御できます。

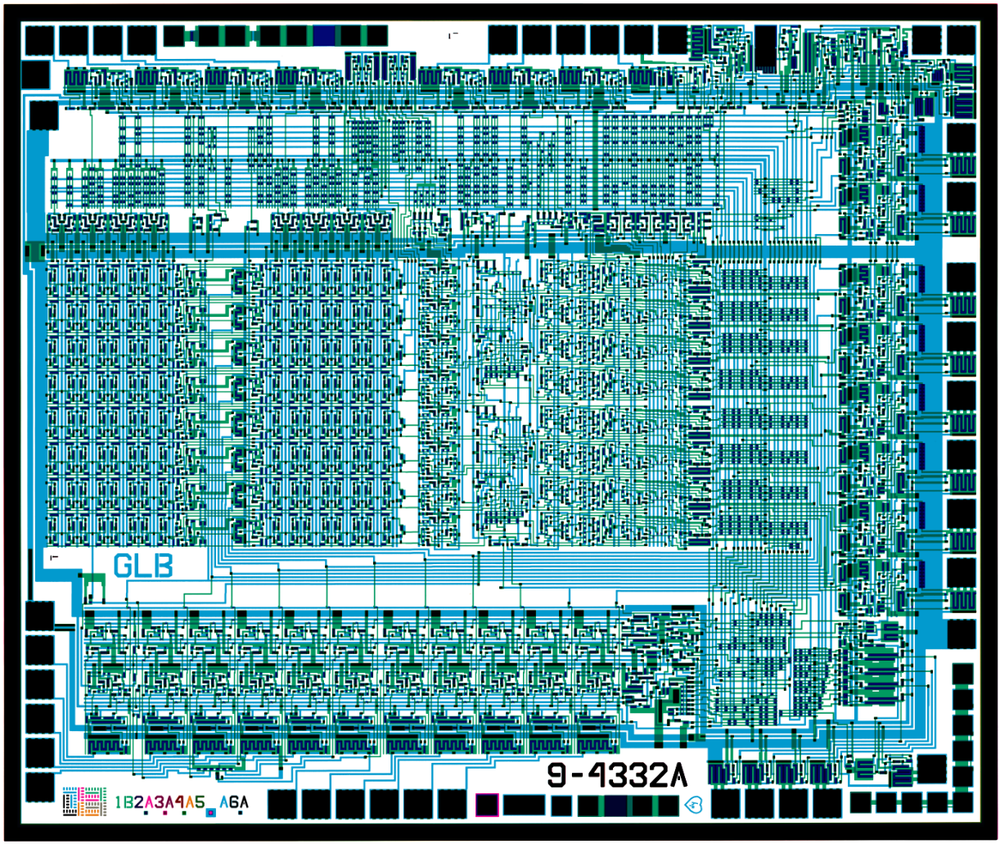

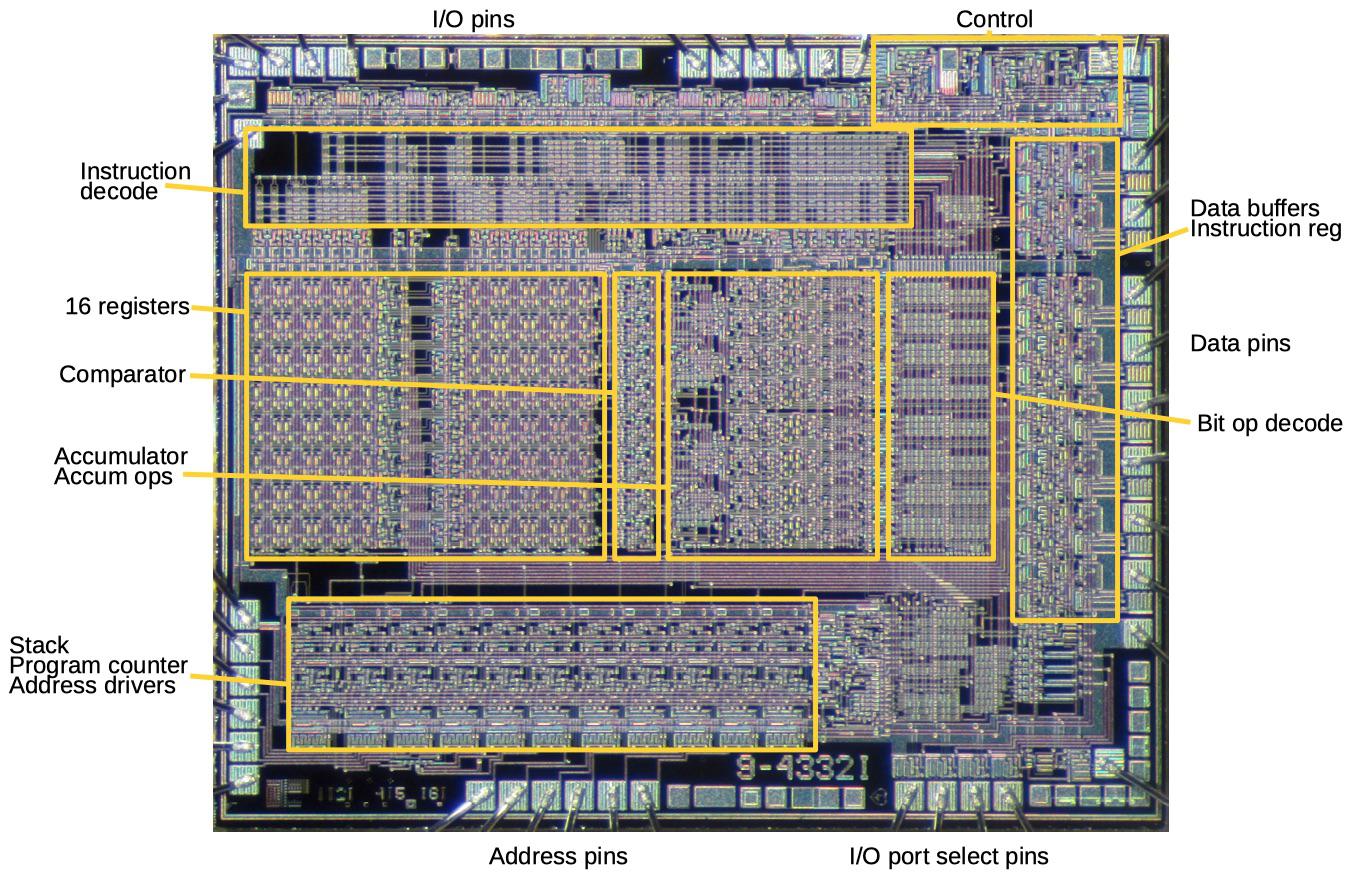

Nanoprocessorは、データストレージを必要としない操作用に設計されているため、メモリ処理をサポートする命令がありませんでした。ただし、一部のアプリケーションでは、ナノプロセッサはRAMをI / Oデバイスとして使用していました。 I / Oポートの1つにアドレスが送信され、もう1つのポートから1バイトのデータが読み取られました。ナノプロセッサー結合フォトマスク(クリック可能) 上記のフォトマスク画像から、ナノプロセッサーは単純であると結論付けることができます。青い線はチップ上部の金属導体、緑の線は不純物を含むシリコンです。周囲の黒い四角-ICの外部接点と通信するための40のサイト。内部の小さな黒い領域はトランジスタです。よく見ると、そのうち4,639個を数えることができます。

命令デコーダーが小さなトランジスターのペアで構成されていることを考慮に入れると、これはコンポーネントの配置の便宜のために行われ、これらのペアを1つとして数えると、3829個のトランジスターが得られます。これらのうち、1061はプルアップであり、2668がアクティブです。比較すると、6502には4,237個のトランジスタがあり、そのうち3,218個がアクティブでした。 8008には3,500個のトランジスタがあり、Motorola6800には4,100個のトランジスタがありました。

以下のブロック図は、ナノプロセッサの内部構造を示しています。真ん中には16個の保持レジスタがあります。コンパレータを使用すると、2つの値を比較して、条件付き分岐を提供できます。制御ロジックユニットは、アキュムレータのインクリメント、デクリメント、シフト、およびビット操作を処理します。標準のALUのような算術演算や論理演算はありません。プログラムカウンタ(右)は、命令レジスタ(左)から命令を取得します。割り込みとサブルーチン呼び出しには、リターンアドレスを格納するための独自の1項目スタックがあります。

Nanoprocessorの説明からの作業のフローチャート

ナノプロセッサは、その単純さと算術演算の欠如にもかかわらず、制御ラインを切り替えるある種の「おもちゃ」プロセッサではないことを強調しておきます。これは、複雑な操作を実行するために使用される高速で強力なプロセッサです。たとえば、HP 98035リアルタイムクロックモジュールは、Nanoprocessorを使用して、2ダースの異なるASCII制御文字列を処理し、1か月の日数をカウントしました。

楽しみのための興味深いプロジェクトは、ナノプロセッサのFPGAバージョンの作成です。ナノプロセッサはおそらく実際の商用プロセッサの最も単純なバージョンであるためです。その手順では、すべてのコマンドについて説明し、実行できるコードの例を示します。

レジスター

下のクリスタルの写真は、ナノプロセッサーのかなりの部分が16個のレジスターによって占められていることを示しています。これらは、データバスを介して残りのコンポーネントと通信します。上部のチェーンは特定のレジスタを選択します。右側のコンパレータの隣にあるレジスタR0。

ナノプロセッサの大部分は16個のレジスタによって占められています。レジスタの

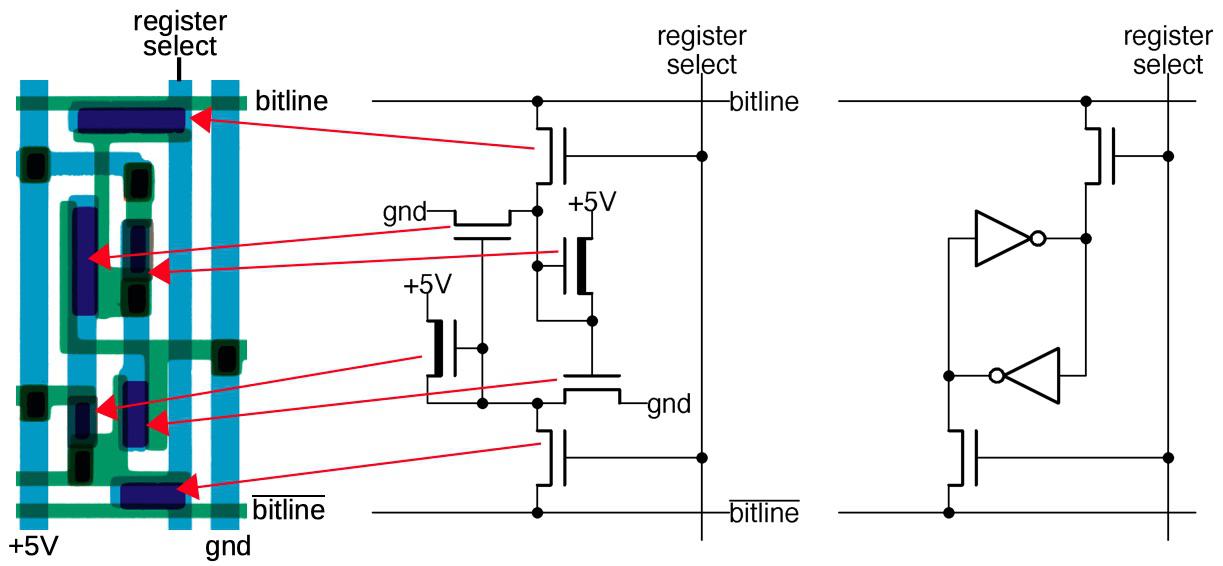

構成要素は、フィードバックループ内の2つのインバータであり、以下に示すように1ビットを格納します。上部導体が0の場合、右側のインバーターは下部導体に1を出力し、左側のインバーターは上部導体に0を出力して、サイクルを完了します。回路は0を「記憶」することで安定した状態を保ちます。同様に、上部導体が1の場合、下部で0に反転され、上部で1に戻ります。ネットはこの方法で0または1を格納でき、1ビットのメモリ位置を形成します。

安定したビット

ストレージ回路内の2つのインバーター次の図は、この2つのインバーターストレージがチップ上にどのように実装されているかを示しています。コンポーネントの物理的な位置は、フォトマスクに基づいて左側に示されています。レイアウトは、セルが占めるスペースができるだけ少なくなるように最適化されています。青い線-金属層、緑-シリコン。中央には、トランジスタを備えた対応する回路の図が示されています。各インバーターは、右に示すように1対のトランジスターで構成されています。上部と下部のトランジスタ-「スルー」、ストレージセルへのアクセスを提供します。

Nanoprocessorに1ビットを保存します。各ビットは6つのトランジスタ(6T SRAMセル)に実装されています。

レジスタセットは、このようなビットセルのマトリックスで構成されます。レジスタ選択バスは、読み取りまたは書き込み用に1つのレジスタ(1列)を選択します。次に、上下のパストランジスタがインバータをそれぞれの水平ビットラインに接続します。読み取りの場合、上のビット行はセルに格納されている値を提供します。レジスタに格納されている8ビットには8ビットの行があります。書き込みの場合、値は上のビットラインに転送され、反転された値は下のビットラインに転送されます。これらの値はインバーターの信号を置き換え、希望の値を取り、このビットを保存します。したがって、水平ビット線と垂直選択線のグリッドにより、値を特定のレジスタに読み書きできます。

デコードコマンド

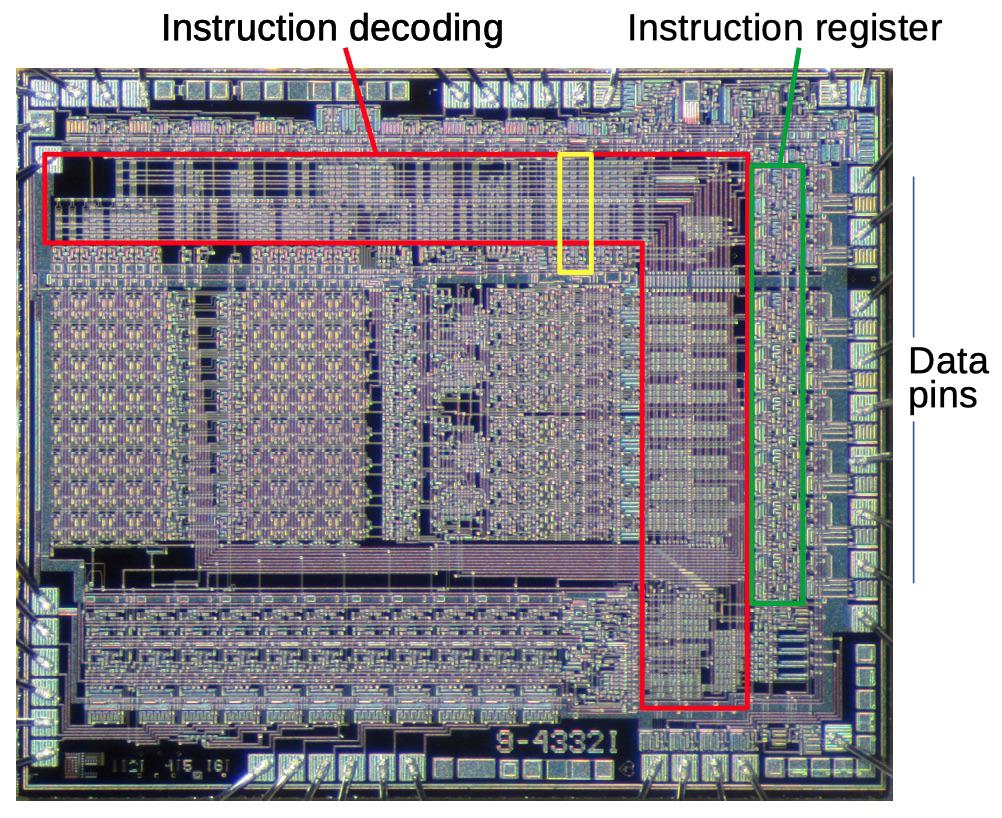

デコード回路は、命令のバイナリコード(たとえば、01101010)を取得し、命令が何であるか(この場合、「レジスタ10からアキュムレータをロードする」)を決定します。多くのプロセッサと比較して、Nanoprocessorの命令は非常に単純です。比較的少なく(48)、命令コードは常に1バイトです。次の図は、命令デコードロジック(赤)がチップのかなりの部分を占めていることを示しています。命令レジスタ(緑)は、現在の命令を保持する8つのラッチのセットです。コマンドレジスタは、コマンドがROMから送信されるデータピンの隣にあります。このセクションでは、黄色で示されているデコードチェーンを分解します。

デコードはNORゲートによって行われます。各NORゲートは、特定のコマンドまたはコマンドのグループを認識します。 NORゲートは、コマンドビットまたはその補数を入力として受け入れます。すべての着信ビットがゼロの場合、NORゲートは一致を報告します。これにより、チーム全体とチームの一部の両方で一致を検索できます。たとえば、コマンド「レジスタRからアキュムレータをロード」のバイナリ形式は0110rrrrで、最後の4ビットが必要なレジスタを示します。 NORゲート(bit7 + bit6 '+ bit5' + bit4) 'はこのコマンドに一致します。

このように構成された命令デコーダーは、コンパクトで反復的な回路から組み立てることができるという点で優れています。これは、PLM(Programmable Logic Array)と呼ばれることがよくあります。マトリックスへの入力信号は水平方向に供給され、出力信号は垂直方向に供給されるという考え方です。各交差点にトランジスタがあり、入力信号はゲートの一部です。トランジスタがない場合、この入力は無視されます。その結果、コンパクトに配置されたNORバルブが得られます。初期のマイクロプロセッサでは、デコーダはしばしばNORゲートのマトリックスから作られていました-たとえば、これは6502の場合でした。

下の図は、右側に3つの拡大されたデコーダーを示しています。これらは、上の図で黄色で囲まれています。この図は、左端のデコーダーに対応しています。図のトランジスタとレイアウトのトランジスタのピンクのスポットの対応に注意してください。入力信号がトランジスタをアクティブにすると、トランジスタが出力をグランドにプルするという考え方です。それ以外の場合、出力は抵抗によってプルアップされます。下部のインバーターは信号を増幅するため、バッテリーの8つの部分すべてに電力を供給するのに十分な電流が流れます。興味深いことに、このレイアウトでは、グランドと出力が接続されたトランジスタのペアを使用しています。単一のトランジスタを使用するよりも利点はありません。いずれにせよ、PLMがどのようにデコーダーの密集した配置を提供するかに注意してください。

命令デコーダのインバータは5Vではなく12Vにプルアップされることに注意してください。これは、ナノプロセッサが、当時の他のマイクロプロセッサに見られるより高度なシリコンゲートトランジスタの代わりに金属ゲートトランジスタを使用するためです。金属ゲートを備えたトランジスタの欠点は、しきい値電圧が高くなることです。そのため、トランジスタの出力電圧は、ゲートの電圧よりもはるかに低くなります。従来のインバータからの出力は、出力電圧が再び低下するため、パススルートランジスタのゲートに供給するには小さすぎます。解決策は、バッテリーパススルートランジスターを制御するデコーダーのインバーターに12 V電源を使用することです。そうすると、信号はパススルートランジスターをアクティブにするのに十分な電圧になります。言い換えると、ナノプロセッサには追加の12 + Vが必要です。より高度なシリコンゲートトランジスタの代わりにメタルゲートトランジスタを使用しているためです。

ナノプロセッサデコーダ回路の1つ。左側の図は、右側に示されている3つのデコーダーの左端のデコーダーに対応しています。

この回路は、アキュムレータ回路に供給される増分/減分信号を生成します。ラングは、クロックジェネレータ、要求、6番目のコマンドビットおよび2番目のコマンドビットの信号レベルが低いときに一致を検出します。一致は、実行フェーズ中にx0xxx0xxとして検出されます。これらのコマンドには、「Increment Binary」(00000000)、「Increment BCD」(00000010)、「Decrement Binary」(00000001)、および「DecrementBCD」(00000011)が含まれます。

図に示されているチェーンは、x0xxx0xxの形式のコマンドとの一致を探します。したがって、一致は、単にインクリメントおよびデクリメントするだけでなく、より多くのコマンドで検出されます。完全に一致するものを探していないのはなぜですか?その理由は、アキュムレータが使用されていない場合、インクリメント/デクリメント信号のアクティブ化は無関係であるためです。一致するオプションのリストを拡張することにより、開発者は回路内のいくつかのトランジスタを取り除くことができます。チェーンが「アキュムレータのクリア」(00000100)や「レジスタからアキュムレータをロード」(0110rrrr)などの他のアキュムレータ関連の命令をオーバーライドすることが重要です。

コンパレータ

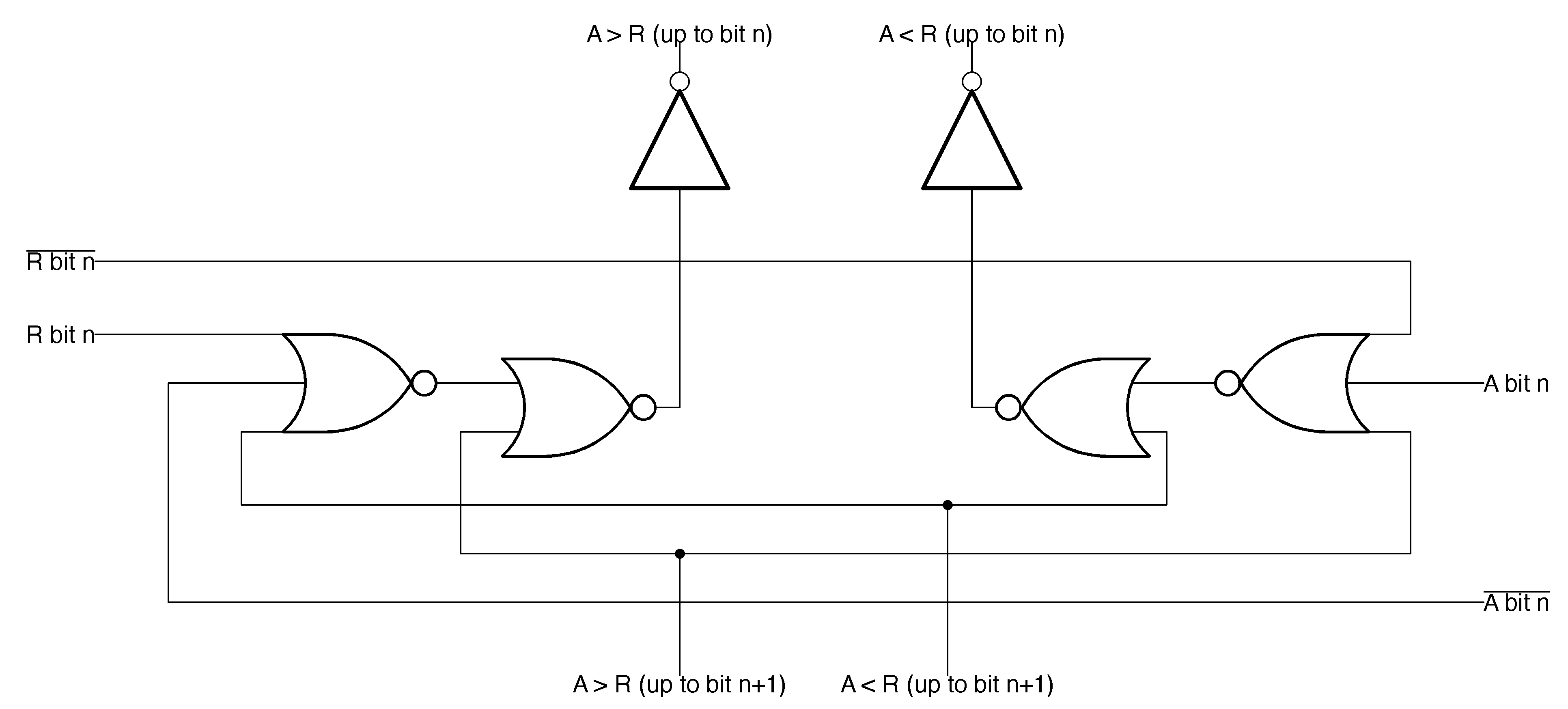

重要なナノプロセッサ回路は、アキュムレータに格納されている値をR0レジスタの値と比較するコンパレータです。コンパレータは、単一のトリッキーな回路を使用してそれらを比較します。基本的に、アルゴリズムは最上位ビットから始まる2つの数値を比較します。ビットが等しい場合は、下位のビットに進みます。最初のビットの差によって、どちらの値が大きいかが決まります(たとえば、10101010と10100111の場合、これは右から4番目のビットを決定します)。

アルゴリズムは、最下位の最上位ビットから始めて、一度に1ステップずつ、8つのステップで実装されます。各ステップは2つの対称部分で構成されます。1つは不等式A> R0が成立するかどうかを判別し、その追加部分は不等式A <R0をチェックします。数値がまだ等しいが、この段階で違いが見つかった場合、段階は「多い」または「少ない」という信号を生成します。それ以外の場合は、決定を下位レベルに渡します。最終決定は最上位のラングによって行われます。コンパレータでの同等性の比較は「無料」で行われることに注意してください-出力に「多い」または「少ない」信号がない場合、値は等しくなります。

8ビットコンパレータのステージの1つ

次の図は、コンパレータの2つのステージの物理的なレイアウトを示しています。コンパレータレイアウトのトリックの1つは、左側のレジスタ0と右側のアキュムレータの間に配置することです。これにより、ワイヤの長さが最小限に抑えられます。コンパレータは、通常のレジスタとデータバス選択パスをバイパスして、レジスタ0に直接アクセスします。

コンパレータの2つのステージ-フォトマスクで指定されているとおり

ナノプロセッサの条件付き分岐コマンドは、コンパレータ出力を検査できます。条件付き分岐回路は非常に単純です。分岐命令の数ビットが、マルチプレクサを介して特定のチェックを選択します。次に、コマンドの7番目のビットで、「trueの場合はこのブランチ」を選択するか、「falseの場合はこのブランチ」を選択するかを決定します。ほとんどのプロセッサとは異なり、Nanoprocessorはどのアドレスへの分岐も許可しません。条件が満たされた場合、2つのコマンドバイトをスキップするだけです(通常、これらの2つのバイトには、目的のターゲットに移動するコマンドが含まれていますが、他のコマンドがある場合もあります)。スキップスキームは単純です。プログラムカウンターが再度呼び出され、値が1ではなく2増加し、2つのコマンドがスキップされます。 Nanoprocessorは、比較的少数のネットに対して広範囲の条件付きチェックを実装していることがわかりました。

ナノプロセッサには、多数の分岐条件があります。このような単純なプロセッサでは驚くほど大きいです。次の条件を確認できます:A> R0、A> = R0、A <R0、A <= R0、A == R0、またはA!= R0。さらに、条件付き分岐は、アキュムレータの値がゼロであるかどうか、アキュムレータに格納されている値の特定のビットがゼロに等しいかどうか、オーバーフローフラグが設定されているかどうか、またはI / Oレジスタの特定のビットが設定されているかどうかによって異なります。

バッテリーと制御ロジックデバイス

アキュムレータは、現在処理中のバイトを格納する特別な8ビットレジスタです。バッテリーの操作は、プロセッサーの説明書では「ナノプロセッサーの心臓部」と呼ばれる制御論理装置(ULU)によって実行されます。 ULUは、ほとんどのプロセッサの算術論理ユニット(ALU)に相当しますが、算術演算または論理演算を実行しないだけです。同時に、ULUは一見しただけでは役に立たないわけではありません。アキュムレータの値を、バイナリまたはバイナリコード化10進(BCD)のいずれかでインクリメントまたはデクリメントできます。 BCDは、1バイトに小数点以下2桁を格納します。これは、I / Oまたはディスプレイに非常に便利なモードです。また、ULUは、アキュムレータのバイナリの補数を検索またはリセットしたり、特定のビットを設定およびクリアしたりできます。最後に、左右のシフト操作をサポートします。

バッテリー関連回路上

の図は、バッテリーとULD回路を示しています。最初のセクションでは、さまざまなネットが配置され、ゼロ値を定義し、BCDをサポートし、キャリースリップを提供します。これは、最下位4ビットからのキャリーの高速生成です。 2番目のセクションには、メインバッテリーとULU回路が含まれています。 3番目のセクションでは、上記のデコードロジックからの制御信号をアキュムレータの8つの部分に分配します。最後のセクションには、ビット操作をデコードし、アキュムレータの目的の部分に信号を送信する命令デコードロジックが含まれています。

アキュムレータ/ ULUの本体は、ビットごとに1つずつ、8つの部分で構成され、最下位ビットが上部にあります。各部分から4つの回路を見ていきます。インクリメント/デクリメント操作用のキャリージェネレーター、インクリメント/デクリメント操作用のビットジェネレーター、新しいアキュムレータ値を選択するためのマルチプレクサ、およびアキュムレータ値が格納されるラッチです。

インクリメント/デクリメントデバイス(下記)の各部分は、半加算器を使用して実装されます。インクリメント/デクリメントチェーンの方向によって、opcodeが決まります。opcodeの下位ビットの0はインクリメントを示し、1はデクリメントを示します。左側のキャリーチェーンはキャリー信号を生成します。インクリメントの場合、キャリー入力が受信され、現在のビットが1の場合、キャリー出力を作成します(それ以降、バイナリ10にインクリメントされます)。デクリメントの場合、キャリーラインはボローを通知するため、キャリー入力(つまり、ボロー)があり、現在のビットが0の場合にキャリー出力が生成され

ます。インクリメント/デクリメントチェーンの一部

右側のラングは、現在のビットをインクリメントまたはデクリメントで更新します。キャリー入力が存在する場合、現在のビットが切り替えられます。基本的に、3つのNORゲートを介したXOR実装です。難しさの1つは、BCDの調整です。 BCDインクリメント操作の場合、桁9がインクリメントされるときにキャリーが発生し、BCDデクリメント操作の場合、桁0はバイナリ1111ではなく9に減少します。

マルチプレクサは、さまざまなバッテリ動作を管理します。動作に応じて、ワンパストランジスタがアクティブになり、目的の値が選択されます。たとえば、インクリメント/デクリメント操作の場合、上位トランジスタは上記のインクリメント/デクリメント回路からの出力を選択します。トランジスタは、対応するインクリメント/デクリメント命令を検出した前述の命令デコーダをアクティブにします。同様に、右シフトコマンドは、各アキュムレータ部分にn + 1個のバッテリビットを適用して値をシフトすることにより、右シフトトランジスタをアクティブにします。

バッテリーの1ビットを格納するラッチとバッテリーの入力を選択するマルチプレクサーの回路

ラッチは、アキュムレータの1ビットを保持します。バッテリーホールドトランジスタがアクティブになると、2つのNORゲートがホールドループを形成します。代わりにバッテリー負荷トランジスタがアクティブになっている場合、バッテリーはマルチプレクサから目的の値をロードします。nビットをクリアしてnビットを設定する行により、コマンドはアキュムレータの個々のビットを変更できます。次に、マルチプレクサはアキュムレータのすべてのビットを一度に更新します。

カウンターとプログラムのアドレス指定

チェーンのもう1つの大きなブロックは、ナノプロセッサの左下隅にある11ビットのプログラムカウンターです。また、このブロックには、サブルーチンからの戻りアドレスを格納するラッチと、中断後にプログラムカウンターを格納する別のラッチがあります。それらを1つの要素の長さのスタックと考えてください。ソフトウェアカウンターには、次のコマンドへの移動を担当する増分デバイスがあります。また、一度に2ずつインクリメントする方法も知っているため、条件付き分岐命令は2つの命令をスキップできます(このようなインクリメントデバイスは、0番目のビットではなく1番目のビットを増やすだけで実装されます)。インクリメントデバイスの動作を高速化するために、キャリーオーバー機能があります。6つの最下位ビットがすべて1の場合、キャリーがすべての最下位ビットを通過するのを待たずに、6番目のビットを一度にインクリメントします。

制御とクロック周波数

Nanoprocessorの最後の部分は制御回路です。他のマイクロプロセッサと比較すると、ナノプロセッサの制御方式はほとんど些細なように見えます。プロセッサは要求クロックから実行クロックに移動し、(定期的な割り込みを使用して)戻ります。制御回路はほんの数個のフリップフロップとゲートであるため、それについて言うことはあまりありません。

結論

次の図は、Nanoprocessorの主な機能ブロックを示しています。ナノプロセッサーは、時代遅れの金属シャッター技術から予想されるよりもはるかにうまく、それらに非常にぴったりとフィットすることができました。リバースエンジニアリングは、これらの機能ブロックがシンプルでありながら注意深く設計された回路で実装されていることを示しています。

ナノプロセッサは金属ゲートトランジスタを使用していましたが、他のマイクロプロセッサは数年前からシリコンゲートトランジスタに切り替え始めています。違いは理解できないように見えるかもしれませんが、コンポーネントの位置に大きな影響を及ぼします。シリコンゲートを備えたトランジスタの製造では、導体を備えたポリシリコンの層が追加されます。その結果、隣接する層を通過できる導体を備えた2つの層があるため、コンポーネントの配置がはるかに簡単になります。金属層しかない場合は、導体が邪魔になるため、コンポーネントを配置するのがはるかに困難になります。私が研究した他のチップでは、メタルゲートトランジスタテクノロジーを使用しました。コンポーネントのレイアウトは嫌だった-各トランジスタに信号をもたらす絡み合ったワイヤーの束は、トランジスタの密度を低く保った。一方、ナノプロセッサの機能ブロックは非常に注意深く設計されており、すべての信号がうまく機能します。たとえば、データバス用に少し余分なスペースがありますが、全体として、ナノプロセッサレイアウトの密度に感銘を受けました。

私のリバースエンジニアリング

ナノプロセッサーに基づくナノプロセッサー機能コンポーネント-プロセッサーは珍しいです。一見、基本的な算術演算がないため、「偽のプロセッサ」のようにさえ思えました。しかし、もっと詳しく調べてみたところ、感動しました。そのシンプルな設計により、当時の他のプロセッサよりも高速に実行できます。コマンドセットは、目に見える以上のことを実行できます。 Hewlett-Packardは、1970年代と1980年代に、文字列の解析や計算の実行など、予想よりも複雑な役割で、多くの製品でNanoprocessorを使用していました。彼のマスクが公開された後、Nanoprocessorが機能したおかげでチェーンのすべての秘密を学ぶことができます。

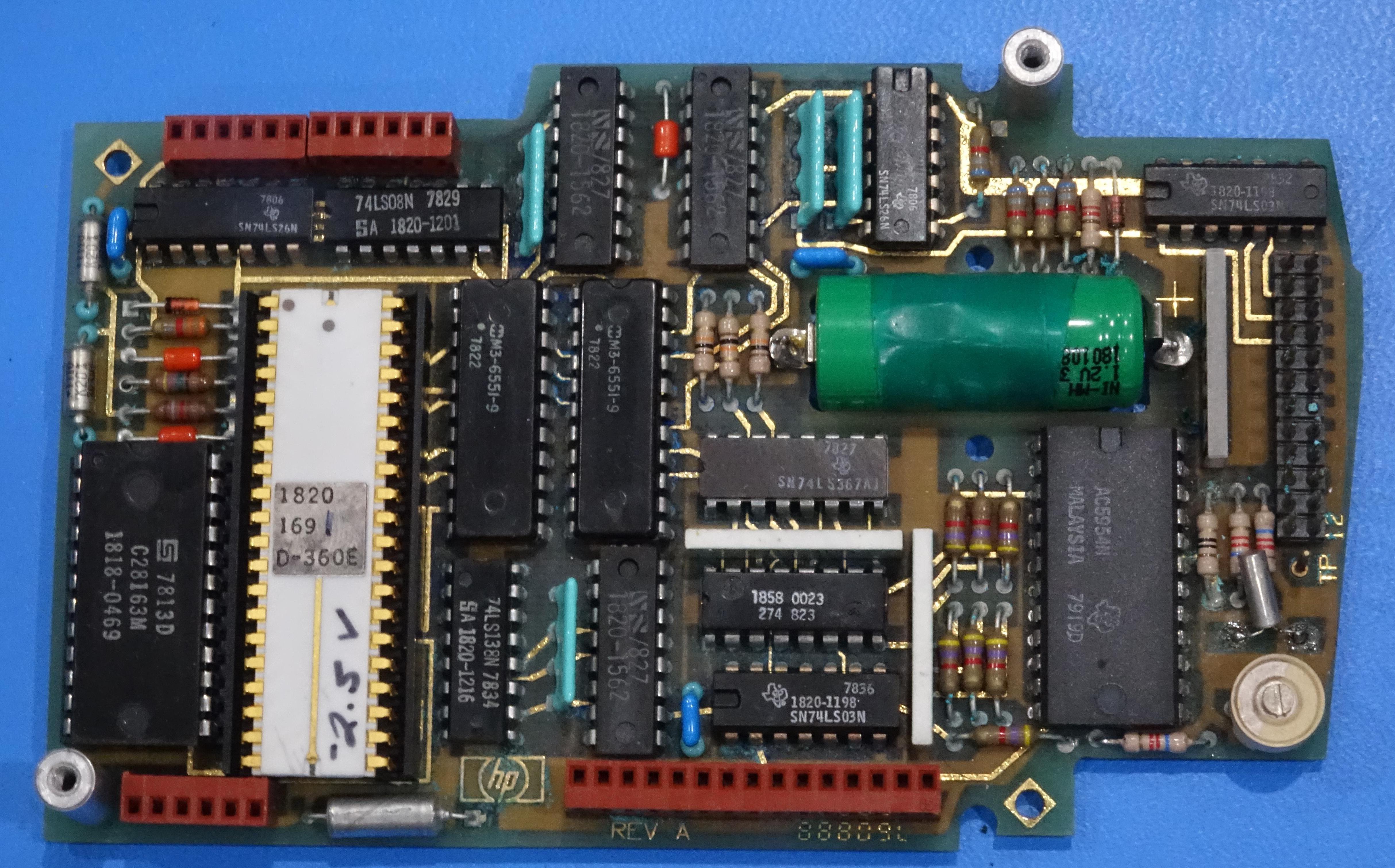

Hewlett-Packard精密タイミングモジュールの一部としてのナノプロセッサ(ホワイトチップ)。手書きの電圧に注意してください。各チップには独自のバイアス電圧が必要でした。