熱の問題の重要性は、Cで温度が10上昇するごとに、故障までの時間が2分の1に短縮されるという単純化されたルールに見ることができます。それは55であれば、ある上チップ65で、10年以上続くに関する計画的陳腐化にプレーしない場合は、多少、チップからの放熱性を向上してわずか5十分な引数へ。このルールは究極の真実とはほど遠いですが、質的には正しいです(たとえば、ここで詳細を読むことができます)。

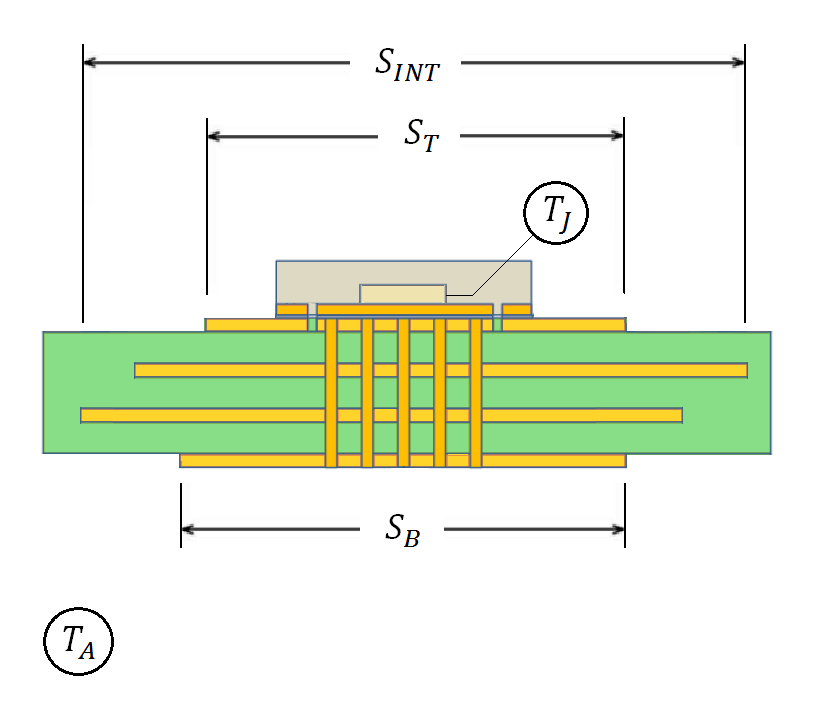

ヒートシンクの配置は、ほとんどの場合、ルーティングを複雑にするオーバーヘッドプロセスであるため、事前に計画する必要があります。これを行うには、プリント回路基板自体がヒートシンクを処理できるかどうかを理解する必要があります。チップメーカーは、ドキュメントにパラメータ「結晶-中」の熱抵抗RθJAを示しています。そうらしい:

見積もりの準備ができました。しかし、これは失礼です、非常に失礼です。熱抵抗はPCBに大きく依存します。そして、示されていることは、標準化されたプリント回路基板での実験で得られたものであり(たとえば、図1のように)、おそらく、得られるものとは大きく異なります。より小さな領域ではるかに優れた熱放散を得ることができるとだけ言いましょう。

何の価値に注意を払っていることは、ダイ・ツー・ボードの熱抵抗RでθJBまたはR θJC(下)。これは開発者に依存せず、本体とその内部設計によって決定されるものです。しかし、ここでは、ほとんどの場合、ケースの選択は熱損失電力によって決定され、主な温度降下はボード上にあります。したがって、ボードを介した熱放散の場合の上記の式を次のように書き直します。

ここで、RθBAは、指定されたパラメータを使用したプリント回路基板の熱抵抗です。この抵抗

この式のすべては問題なく(変更されたベッセル関数を除く)、対流のある1つの表面(ルートの「2」を削除)で解くことができますが、ほとんどの場合、ボードのみが半径方向の対称性がなく、均一ではありませんが、内部に沿って不均一に熱が供給されます半径。したがって、適応する必要があります。最初の2つの質問は、同じ面積の均質な特性を持つ環状ゾーンに分割することで解決されます。後者を解決するには、熱抵抗回路の近似モデルを作成する必要があります。図3は、元の記事で提案された内容を示しています。ボードを3つのゾーンに分割することを提案します。マイクロサーキットの下のゾーン、外層にポリゴンがあるゾーン、および内層にポリゴンのみがあるゾーンです。マイクロ回路に直接接続されている導体のみが考慮されます(条件付きで「リンギング」)。

上部と下部のポリゴンを平均し、平均金属化面積を取ることが提案されています。これらの層の熱放散への影響は明らかに異なり、さらに面積が大きく異なる可能性があるため、私はこれに本当に同意しません(下の層は面積が大きくなることがよくあります)。そのため、ボードを上半分と下半分に分割し、各部分の計算を個別に行いました。

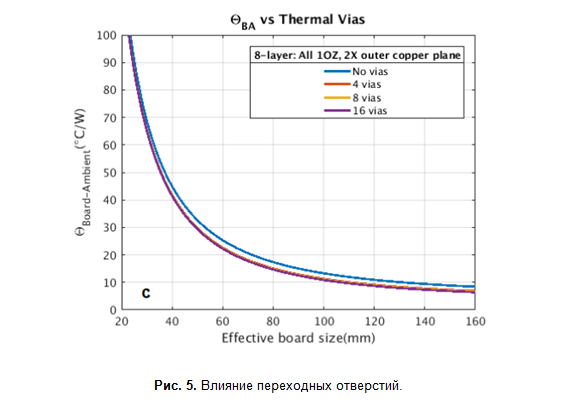

この記事には、さまざまなパラメータの影響を受けた多くのグラフが含まれているので、それらを見ると便利です。これらのグラフでボードを分割するアプローチを調整しました(図4)。これらはそれぞれQFN5X5、QFN6X6、およびQFN3X3パッケージ用です。ボードが非常に大きい場合、グラフはビアの熱抵抗に関連する制限に「該当」しますが、それらのパラメータは指定されていません。充填せずに、直径450ミクロン、壁厚20ミクロンを使用しました。

モデルには相関関係があることがわかりますが、すべての入力データがまだ欠落しているため、100%の一致を達成しようとはしませんでした。さらに、ビアには奇妙な瞬間があり(図5)、ビアがなくても熱抵抗にはほとんど影響しません。これはあまり直感的ではありません。

図4の下のグラフでも、2行のデータを見ることができます。2つの方法で2ゾーンモデルをカウントしました。記事AND8222 / Dで説明されているようにマトリックス乗算を使用し、図3のようにモデルを使用して、マイクロサーキットの下のゾーンのみを破棄します(抵抗には寄与しません)。記事のグラフは、ビアの影響がないかのように、ほぼ同じ漸近になっていることがわかります。これは私にとって、ビアの影響を考慮に入れて、モデルに何か問題があるという別の要因になりました(または私は何かを理解していません)。

計算機は、少なくともさまざまなパラメータの影響に関する定性的なアイデアから定量的な見積もりに移行することを可能にしたという意味で有用であることが判明しました。ボードの熱抵抗は10 °の領域に駆動できると結論付けることができます。自然対流でもC / W。散逸には2〜3Wで十分です。もう1つの有用な注意点は、マイクロ回路に直接接続されている金属だけがヒートシンクで重要な役割を果たすということです。もちろん、ボード内の銅の体積比率が大きいほど、実効熱伝導率は高くなります。この計算機に基づいて、マイクロ回路上のヒートシンクとケースへのヒートシンクの存在を増やすことができます。これも行います。何か面白いことがあれば、次の出版物で共有します。