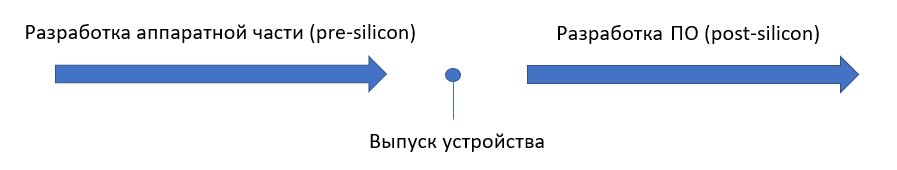

たとえば、SoC(System on Chip)や、多くの統合デバイスが搭載されたプリント回路ボードなど、最も単純ではないデバイスのモデルを使用することについて説明します。これらのデバイス自体の開発では、2つの段階を区別できます。ハードウェアが最初に開発されます。これは遅いプロセスです。1年以上かかる場合があります。

物理デバイスの最初のリビジョンが表示され、基本的なチェックが実行された後、デバイスはソフトウェア開発者に転送されます。この瞬間から、第2フェーズ、つまりデバイス用のソフトウェアの開発が始まります。これらは、さまざまなオペレーティングシステム用のファームウェア、BIOS、BSP / CSP(ボードおよびCPUサポートパッケージ)、およびドライバーです。

ちなみに、チップの開発では、しばしば「シリコン」と呼ばれ、これらのフェーズは「プレシリコン」と「ポストシリコン」または単に「シリコン」と呼ばれます。

理論的には、物理デバイスが表示される前にソフトウェア開発が可能です。ただし、実際には、そうする人はほとんどいません。中間の起動やデバッグの可能性のない開発、そしてこれはまさにデバイスが必要とされるものであり、非常にありがたい仕事です、私はそのようなマゾヒストに会ったことがありません。誰もが「ハードウェア」を待っていますが、先ほど書いたように、1年で登場します。

その上、ハードウェアには別の問題があります。最初の改訂版は限定版で発行され、一度に1つずつ配布されます。簡単に言えば、誰にとっても十分なボードとチップがありません。待ち行列、衝突があります、それは攻撃になります。また、誤ってデバイスを焼き付けた場合、これは非常に簡単です。別のデバイスが見つかるまで、すべての開発が停止します。多くの場合、見つからないため、新しいものを作成してから、配信を待つ必要があります。これにより、プロセスが大幅に遅くなります。

そして、シミュレーターはソフトウェア開発者の助けになります!

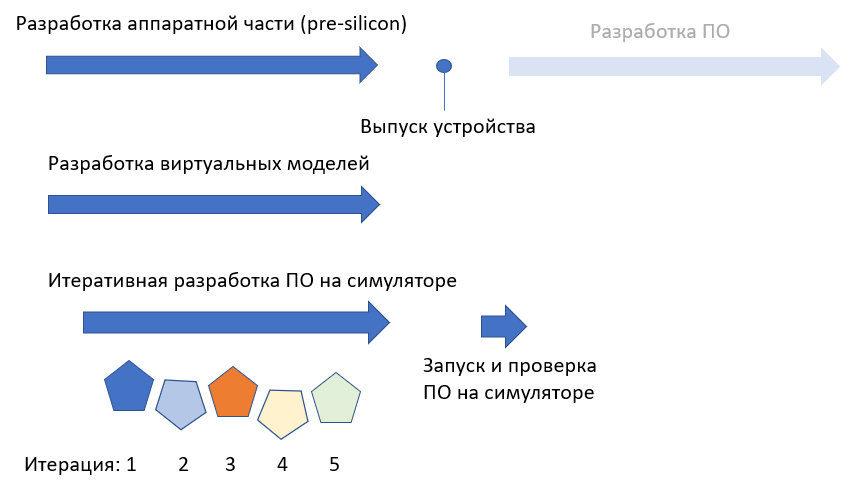

仮想デバイスモデルの作成は、物理デバイスの設計と同時に開始されます。しかし、モデルの作成とリリースははるかに簡単であるため、そのようなモデルの最初のリリースは、従来、1年ではなく、はるかに早く表示されます。このようなモデルを使用すると、ソフトウェア開発者は「ハードウェア」を待たずにすぐにタスクを開始できます。

はい、すべての機能があるわけではありませんが、最初の段階のプログラマーはすべての機能を必要としません。デバイスが作成されるまで、ハードウェアアーキテクト、モデラー、およびソフトウェア開発者のチームは、どの特定の機能をどの段階で実行する必要があるかを反映する明確で一貫した計画を立てる必要があります。各反復および各段階で、仮想モデルは追加機能とともに成長します。追加機能は、ソフトウェア開発者がこの特定の機能のドライバーを作成したり、ファームウェアを作成したりするために使用されます。

このアプローチでは、モデルとソフトウェアの開発者は共通の仕様を使用します。モデル上でソフトウェアを実行することにより、彼らは本質的にお互いの仕事をチェックしています。

追加のプラスは、ハードウェア自体がまだそこにないという事実にもかかわらず、「ハードウェア」の検証です。一見意外に聞こえますが、ここでは、デバイスの設計におけるアーキテクチャ上のエラーについて説明します。その一部は、モデルでソフトウェアを実行するときに検出できます。そして、リリースされる前にハードウェアのこれらのバグを修正することが可能であるため、これは非常にクールです。そうでなければ、これらのエラーは次のリビジョンを再発行する必要につながり、これは非常に高価な喜びです。

着信データストリームを処理するための10ブロックが複雑なデバイスに実装されていて、制御レジスタと管理レジスタによってそれらの半分だけで作業できる場合がありました。これは以前のバージョンのデバイスに実装されており、アーキテクトはこの部分を拡張するのを単に忘れていました。モデルを作成し、他のチームがドライバーを作成して実行したところ、すべての高度な機能が利用できないことがすぐにわかりました。アーキテクチャと仕様は、デバイスの物理的なプロトタイプが作成される前に修正されました。

大規模なデバイス企業は、自社製品を中心に構築されたエコシステム全体をサポートできます。このエコシステムには、この機器用のソフトウェアを製造している企業を含む、他の多くの企業が含まれています。たとえば、これらはBIOSメーカー、いわゆるIBV(Independent BIOS Vendors)であり、その中で最も有名なのはAMI、Insyde、Phoenixです。このような企業は、ハードウェアメーカーからモデルを受け取り、物理デバイスが登場する前に開発を開始します。たとえば、Intelプラットフォームの場合、Simicsシミュレーターが使用されます。これについては、Ecosystem Partners Shift Left with Intel for Faster Time-to-Marketの記事で詳しく読むことができます。

モデルの作成には追加のコストが必要であることは明らかです。もちろん、コストの額はモデルのタイプ(機能、サイクルごとなど)によって異なりますが、一般に、モデルの作成コストは、デバイスのソフトウェアを作成するコストとほぼ同じであると見なすことができます。すべての企業が以前のリリースにこの価格を支払う用意があるわけではありません。そのため、このアプローチは大企業で一般的です。彼らはこれに十分な予算を持っており、市場での製品の早期発売は彼らの収入を大幅に増加させます。最近ではありますが、ソフトウェア開発や小規模企業でシミュレーターがより広く使用される傾向にあります。

多くの場合、コストを削減するために、モデルはすべての可能な機能を実装するのではなく、デバイスを使用する特定のシナリオに必要な最小限の機能のみを実装します。たとえば、ネットワークデバイスをVLANで使用する予定がなく、ファームウェアを更新してtftp経由でダウンロードするだけの場合、VLANタグを使用してロジックを実装する必要はありませんが、ネットワークを介したデバイスの起動とファームウェアの更新のシナリオの機能を完全に実装する必要があります。ボリューム。

最終結果は何ですか?

ハードウェアとソフトウェアの開発時間がほぼ等しいと仮定すると(上の図を参照)、モデルを使用すると、製品の販売にかかる時間を大幅に、ほぼ2倍短縮できます(いわゆるTTM-市場投入までの時間)。 、「ハードウェア」とソフトウェアの開発は、順次ではなく並行して行われるため。このため、Shift Leftという用語がよく使用されます。これは、テストの分野に由来し、可能な限り早期にテストすることを意味します。同じ用語がソフトウェア開発にも当てはまります。ソフトウェア開発は、シミュレーターで実行するとタイムラインの左にシフトするように見えます。

機器の最初のリビジョンが表示されるまでに、実際のハードウェアでのソフトウェアの操作性を確認するだけで済みます。理想的には、エラーと修正は重大ではなく、コードはモデル上ですでに記述およびデバッグされているため、この段階で大きな遅延が発生することはありません。

このアプローチは「無料」ではなく、追加の予算とプログラマーのチームが必要になるため、これらのコストがいずれかの場合にどの程度の利益をもたらすかを明確に理解する必要があります。

シミュレーターの使用例はこれだけではありません。次の記事では、建築研究と複雑な環境の作成について説明します。切り替えないでください。