IBM は、2nmプロセス技術の開発を発表しました。

発表内容:

- 2nm。

- 釘の大きさの領域に500億個のトランジスタ。その後、彼らは、150平方ミリメートルの面積で、つまり、1平方ミリメートルあたり3億3300万個のトランジスタを明らかにしました(

- MTx / mm 2)。

- トランジスタ(接触ポリピッチ、CPP)のゲートピッチは44 nm、ゲート長は12nmです。

- (Gate All Around, GAA). – , IBM (horizontal nanosheets, HNS).

- HNS .

- 45% 75% 7 .

- (EUV) HNS 15 70 . , SRAM.

- 5 .

これは本当に2nmのプロセス技術ですか?今日、TSMCはチップ生産のリーダーです。決定係数0.99で曲線を近似することにより、TSMCプロセス名とトランジスタ密度の関係をプロットしました。

28nmから5nmまで、実際の数値はICKnowledgeとTechInsightsに従って使用されます。 3nmの数値は、TSMCのプレスリリースに基づいています。 2nmと1.5nmが外挿です。

グラフを使用して、トランジスタの密度を同等のTSMCプロセステクノロジ(TSMC同等ノードまたはTEN)に変換できます。私たちは、333 MTX / mmのために2.9ナノメートルを取得します 2。私たちの観点からは、これは2nmではなく3nmのプロセス技術であることがわかります。

IBMからの発表を、3nmプロセス技術および提案された2nmプロセスの以前の発表とより詳細に比較するには、いくつかの仮定を行う必要があります。

- 発表から、CPPは44nmであることがわかっています。

- 生産が最もタイトなトランジスタ配置技術であるSingleDiffusion Break(SDB)を使用していると仮定します。

- 発表の切り取り写真に基づくと、Buried Power Rails(BPR)テクノロジーは使用されていません。BPRは、HNSトラックサイズを5.0に減らすために必要です。したがって、このプロセスでは、この値が6.0であると想定します。

- 333 MTx / mm 2の密度を達成するには、最小金属ピッチを18 nmにする必要があります。これは非常に攻撃的な値であり、おそらくEUVマルチマトリックスフォトリソグラフィーが必要になります。

2nmIBMと既存の3nmプロセステクノロジー

次の表は、IBMの設計をSamsungおよびTSMCからの3nmプロセスの見積もりと比較しています。サムスンもHNSと連携しており、TSMCは3nmFinFETに落ち着きました。サムスンとTSMCはまた、プロセス技術のトランジスタ密度が5nmと比較して3nm増加したことを発表しました。したがって、3社すべてのトランジスタの密度がわかっており、すべてのTENを計算できます。 IBMのTENは2.9です。 Samsungには4.7があり、TSMCには3.0があることがわかります。繰り返しになりますが、IBMの2nmはTSMCの3nmに似ていますが、Samsungは遅れています。

すべての企業がSDBテクノロジーを使用していると仮定すると、発表された密度を達成するために必要な指標パラメーターは赤で強調表示されます。FinFETにBPRがないとこのパラメータは5.0に達する可能性があるため、トラックの高さはTSMCで最小ですが、HNSを同じ高さにするには、BPRを使用する必要があります。

2nmIBMと既存の2nmプロセステクノロジー

次の表では、SamsungとTSMCの2nmプロセステクノロジーのパラメーター値を推定しました。私たちの外挿では、企業がBPRを使用していると想定しています(BPRテクノロジーはまだ成熟していませんが、2023- 2024年に2nmプロセスを発表したときにオンラインになる可能性があります)。また、企業がNHSフォークシート(HNS FS)アーキテクチャを採用して、4.33のトラック高さを達成するとします。CPPおよびMPPの見積もりは、テクノロジーの小型化における現在の傾向に基づいています。

消費電力とパフォーマンス

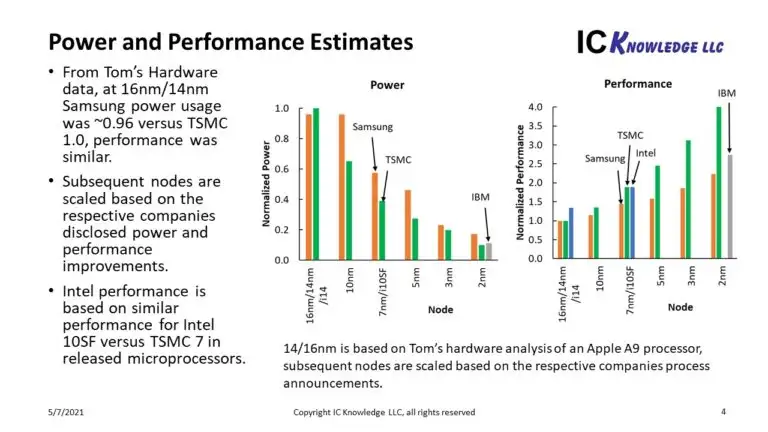

今年 は、Intelの追加のパフォーマンスデータを使用して、SamsungとTSMCのデバイスの消費電力とパフォーマンスについてすでに推測しました。外挿は、企業からの保証と、14nmプロセスと16nmプロセスの実際の比較に基づいています。

IBMは、消費電力とパフォーマンスの改善を高度な7nm製造プロセスと比較しているので、それらのデータを同じグラフにプロットできます。

IBMは、HNSを使用することで大幅な電力節約を実現し、SamsungやTSMCの3nmプロセスよりも2nmプロセスの効率を高めています。私たちの意見では、TSMCが2 nmでHNSに切り替わるとき、それらの消費電力はIBMの消費電力に劣ることはありません。パフォーマンスに関しては、TSMCの3nmプロセスがIBMの2nmプロセスを上回ると想定しています。

もちろん、これらはすべて、多数の仮定に基づく単なる見積もりです。

結論

IBMの発表を分析した結果、2 nmプロセステクノロジーは、トランジスタの密度の点でTSMCの3 nmプロセステクノロジーに似ているが、消費電力インジケーターは最高ですが、速度は劣っていると結論付けました。IBMの声明は印象的ですが、これは単なる実験室のサンプルであり、消費電力のみでTSMCから3nmを明らかに上回っています。同時に、TSMCからの3 nmデバイスの最初の危険なバッチが今年登場し、商用のものが来年登場します。

私たちの意見では、TSMCは、2023-2024に生産が開始されたときに、2nmプロセス技術に基づくデバイスの密度、消費電力、および速度の利点を維持します。