、話は2015年に始まります。FPGAについて知ったときです。最初の簡単な作業では、カウンターから必要なクロックを形成し、そこからすべてのロジックを供給しました(当然、FPGAに供給されるよりも遅いクロック(たとえば、UARTやSPIなど)が必要な場合)。当然、彼らは私を追いかけましたが、私は「しかしそれはうまくいく!」という簡単な言い訳があり、すべてが本当にうまくいきました。それ以来、「どこからタイミング信号を得ることができるのか」という考えが頭に残りました。

ソースが細断処理するためのオプションは多くありません。 PLLまたはMMCMに基づいて特定のClockWizardから取得するか、カウンターから生成するか、いわばシングルエンドの脚から直接生成します。 FPGAプリミティブによって生成されたクロック信号を取得するとどうなりますか?

この記事の一部として、マルチプレクサ(MUXF7)、真理値表(LUT1)の3つのオプションを検討し、FPGAレッグをそれら自体に短絡させることにしました。

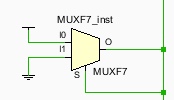

マルチプレクサの場合、出力は制御信号に供給され、入力信号は0と1にプルされます。

LUTの場合、出力を入力に短絡し、反転真理値表を設定します。「1」を供給するとゼロを出力し、「0」を供給すると1を出力します。

GPIOの場合、すべてが単純で、出力信号には入力信号の逆が割り当てられます。

| s2 =〜s1を割り当てます。 |

実験の目的: 3つの方法で周波数を生成して測定すること。

カウンターを犠牲にして周波数を測定します。カウンターは4つあります。オプションごとに3つ、基本的なカウンターが1つあります。これに対してすべてがカウントされます。そして、ChipScopeを通じてこれらのカウンターを監視します。

そして、これがモジュールコード全体です:

module gen_clk(

input clk_base,

input s1, //gpio

output s2 //gpio

);

// -

assign s2 = ~s1;

wire clk_gpio = s1;

reg [31:0] cnt_gpio = 0;

(* MARK_DEBUG="true" *) reg [31:0] cnt_gpio_buf = 0;

always@(posedge clk_gpio)

begin

if(cnt_gpio[2:0]==3'd0) cnt_gpio_buf<=cnt_gpio;

cnt_gpio <= cnt_gpio + 1'b1;

end

//

wire clk_mux;

MUXF7 MUXF7_inst

(

.O(clk_mux),

.I0(1'b1),

.I1(1'b0),

.S(clk_mux)

);

reg [31:0] cnt_mux = 0;

(* MARK_DEBUG="true" *) reg [31:0] cnt_mux_buf = 0;

always@(posedge clk_mux)

begin

if(cnt_mux[2:0]==3'd0) cnt_mux_buf<=cnt_mux;

cnt_mux <= cnt_mux + 1'b1;

end

//

wire clk_lut;

LUT1#(

.INIT(2'b01)

)

LUT1_inst(

.O(clk_lut),

.I0(clk_lut)

);

reg [31:0] cnt_lut = 0;

(* MARK_DEBUG="true" *) reg [31:0] cnt_lut_buf = 0;

always@(posedge clk_lut)

begin

if(cnt_lut[2:0]==3'd0) cnt_lut_buf<=cnt_lut;

cnt_lut <= cnt_lut + 1'b1;

end

//

(* MARK_DEBUG="true" *) reg [31:0] cnt_base = 'd0;

always@(posedge clk_base)

begin

cnt_base <= cnt_base + 1'b1;

end

endmodule

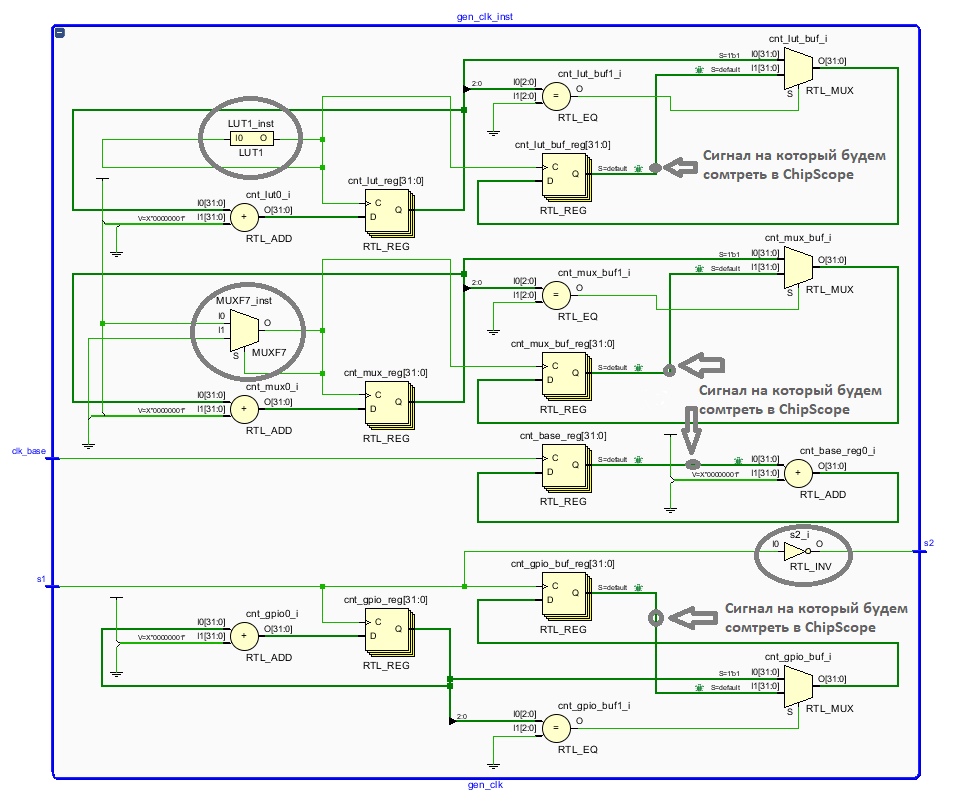

これがプロジェクトの概略図です。プリミティブは丸で囲まれ、矢印は周波数分析のためにChipScopeに入力される信号を示します。

実用的な部分

3つのボードを自由に使用できます。

- KC705評価キット

- ML507評価キット

- 中国のSpartan-6 XC6SLX16ボード

今後の展望先を見据えて、最後のボードは正常な結果を持っていなかったと言います。

そして今、実際の結果

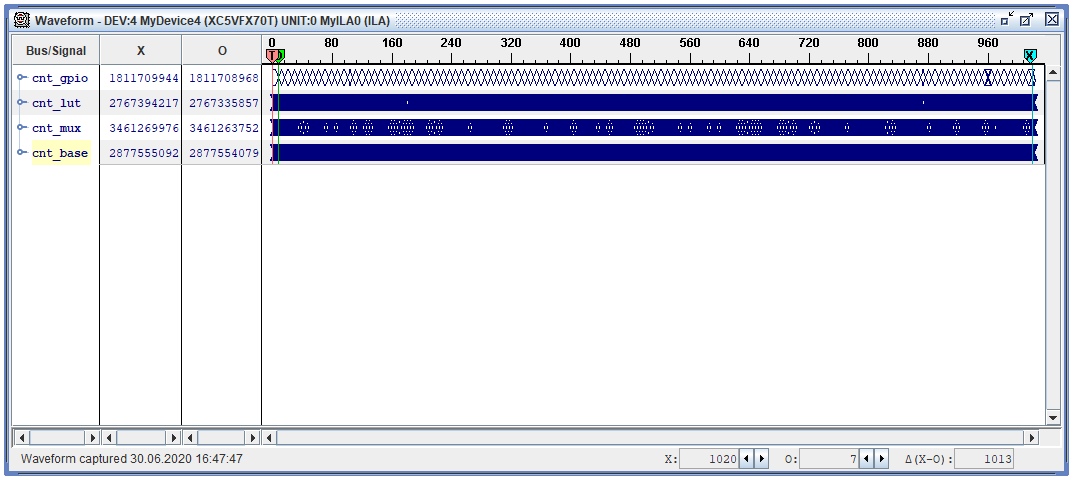

Kintex-7:

プロジェクトはそのために作成され始めたので、プロジェクトは一度に完全に作成されたのではなく、段階的に作成されました。まず、1つのLUTを接続し、デバッグに信号を追加して監視を開始しました。

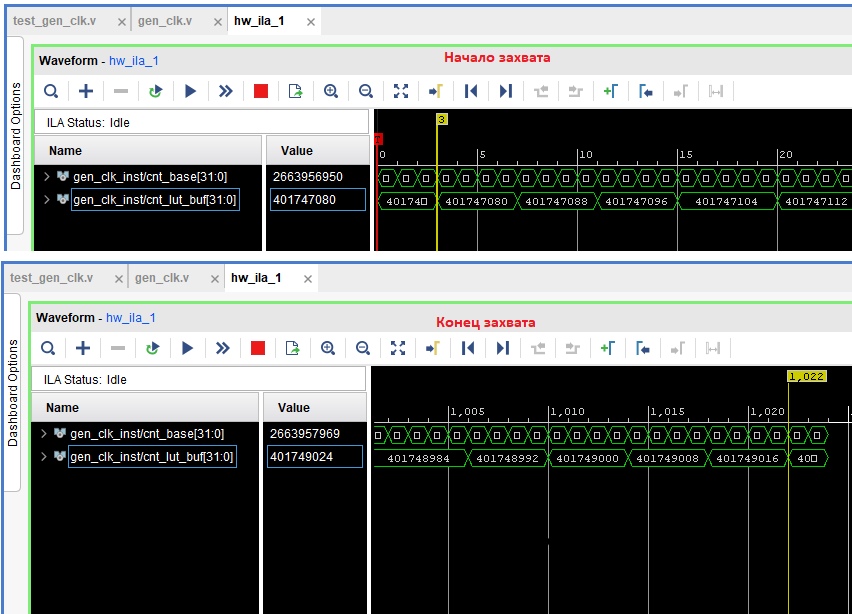

ベースカウンターは200 MHzでクロックされるため、ルートで生成されるクロックの周波数を計算することは難しくありません。ルートカウンターのデルタカウンターが基本カウンターのデルタである回数は、その頻度の何倍かです。この場合:戦利品によって生成される周波数は381.55 MHzです。

次に、プロジェクトにマルチプレクサを追加します。1つのルートと同様に、それとルートの周波数を計算します(結局、何かを変更する必要があります)。

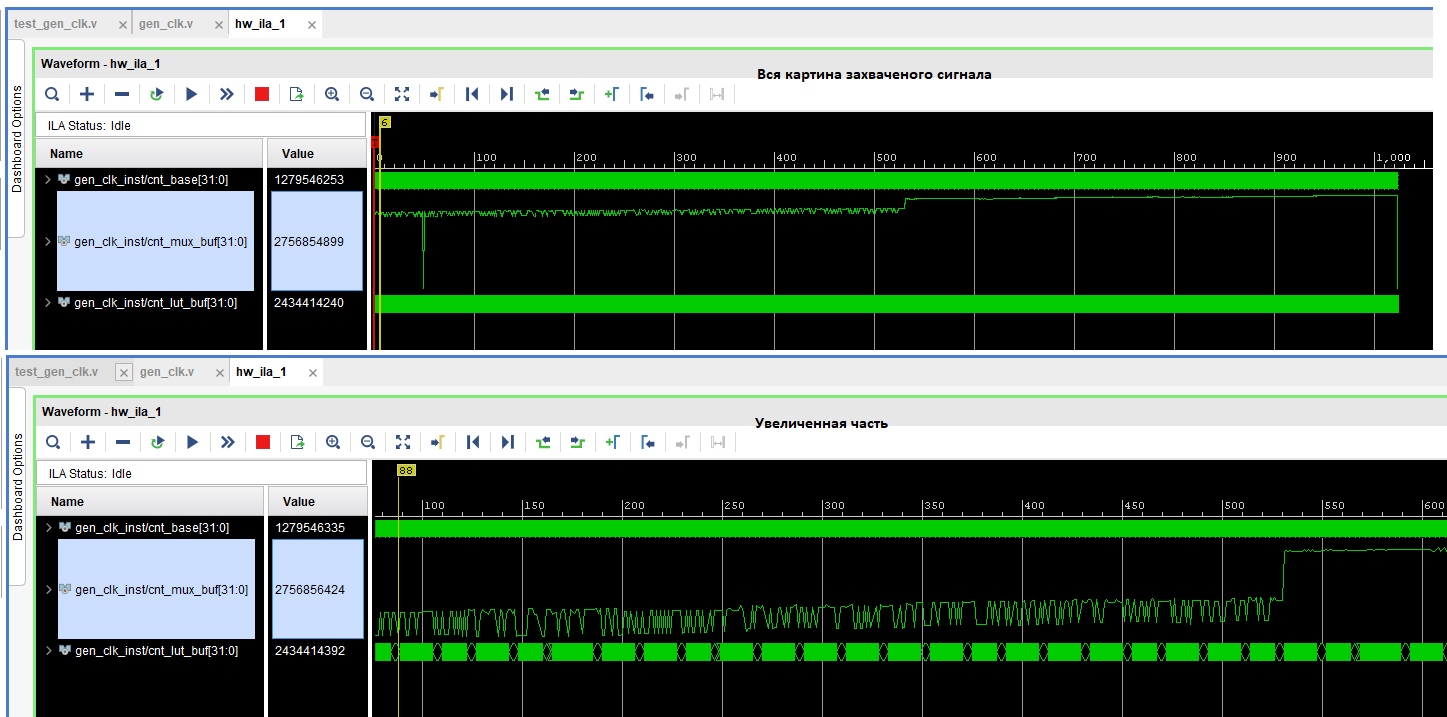

一目でわかる最初のことは、カウンターがどれだけガタガタと音を立てるかです。これはマルチプレクサーの巨大な周波数に影響しますが、一般的にはカウンターが増加していることは明らかです。つまり、カウンターを取得してカウントすることもできます。最終的に:

- マルチプレクサー周波数:5953.89 MHz

- 戦利品周波数(変更):379.98 MHz

最後に、GPIOペアからプロジェクトに閉ループを追加しましょう。KC705ボードには、SMAコネクタJ13およびJ14があります。ここでは、長さ約10 cmの導体でそれらを閉じました。

- GPIO周波数:90.59 MHz

- マルチプレクサ周波数:12994.13 MHz

- 戦利品周波数:380.18 MHz

実験のために、導体をより長いものに置き換えましょう。ワイヤは2倍です。その結果、周波数は85.29 MHzに低下しました。

実験のこの段階では、FPGAのプリミティブの動作周波数が同じではないことに注意してください。戦利品が1つしかない場合、シンセサイザは最速の戦利品を選択してその周りに回路を構築し、マルチプレクサが追加されたとき、シンセサイザは戦利品とマルチプレクサの両方が可能な限り高速に動作するスーパーポジションを見つけようとしましたが、これらはすでに他の要素と周波数が遅くなっています。外部ピンが追加されたとき、クリスタル上のプロジェクト全体は基本的にこれらのレッグに再配置され、プロジェクトは近くの要素で合成され始めました、何らかの理由で、その場所で戦利品とマルチプレクサーの周波数が著しく増加しましたが、プロジェクトに対するこのすべての背景に対してそれを忘れないでください深度が1024でデータバスが64〜128のChipScopeが接続されている(プロジェクトごとに異なる)。次のボードに移りましょう。

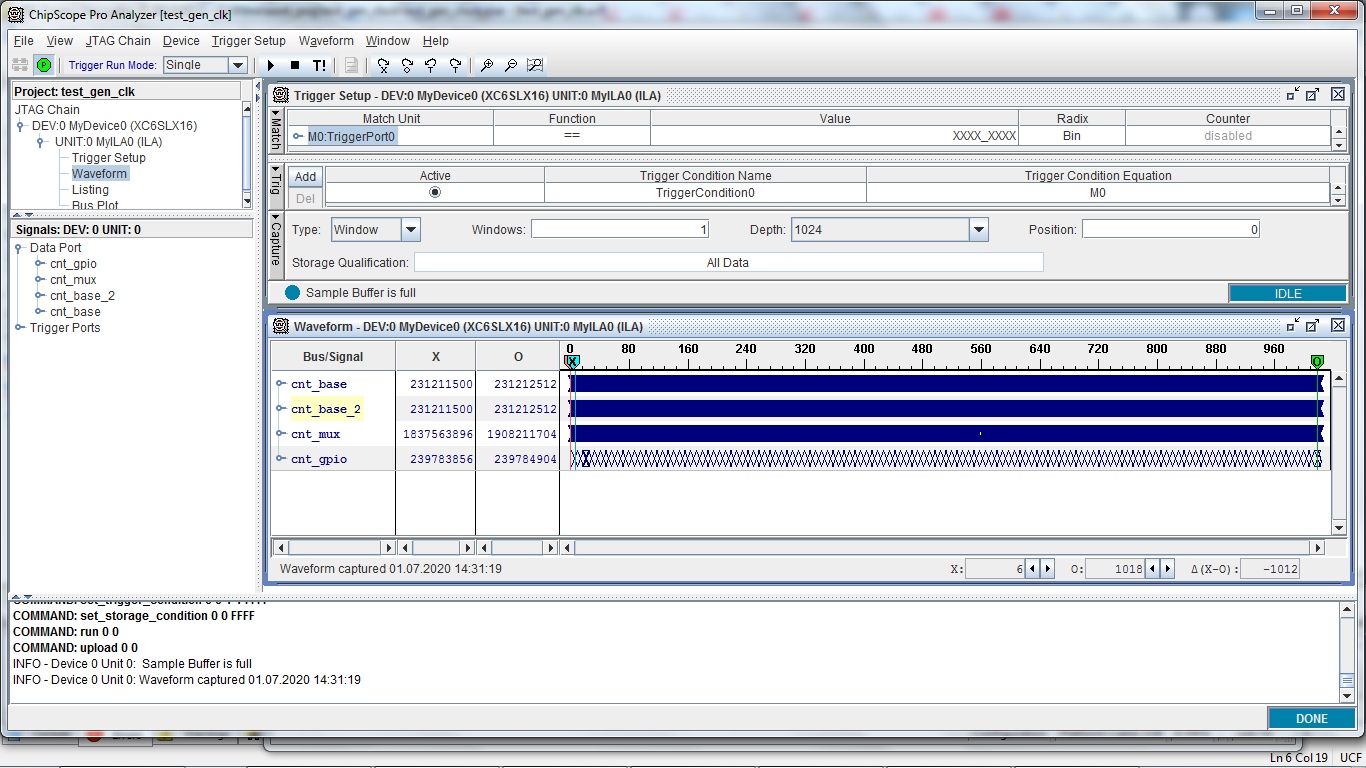

Virtex-5:

私は以前のボードで行った方法のすべてを行ったのではなく、すぐにマントを生成するための3つのオプションすべてを追加し、ChipScopeで何が起こったかを調べました。

図は2つのラベルXとOを示しています。列の値と同様に、数値の形式は符号なし10進数です。ベースカウンターが100 MHzでカウントするようになったことは注目に値します。そしてその結果:

- GPIO周波数:96.34 MHz

- マルチプレクサー周波数:614.41 MHz

- 戦利品周波数:5761.1 MHz

このボードでは、ルートがマルチプレクサよりも速く、ピンの周波数が最初のボードよりも高いことがわかりました。これは、2つのピンを10 cmの導体ではなくジャンパで接続したため、結果として通信ラインが短くなり、周波数が高くなったためと考えられます。

そして今、中国のボードの最後のオプションです。

Spartan-6:

ChipScopeには2つの基本的なカウンターがありますが、実際には、ChipScopeを再構成したくない同じカウンターです。このプロジェクトでは、基本的なカウンターは50 MHzでクロックされます。

このボードの場合、すべてがはるかに複雑であることがわかりました。まず、プロジェクトは、以前のバージョンで合成された形式で合成されることを望まなかった。次に、最終的にはLUTを破棄する必要があり、5ウェイのLUTに置き換えようとしましたが、うまくいきませんでした。一般的に、結果は次のとおりです。

- GPIO周波数:51.77 MHz

- マルチプレクサ周波数:3 490 504 MHz

- 戦利品の頻度:収集に失敗しました

このボードのパフォーマンスの結果はまったく満足のいくものではありませんでした。また、戦利品をチャンクとして使用できなかっただけでなく、マルチプレクサの信じられないほど巨大な周波数が原因でした。足に発生する細断は25〜30cm程度の導体を使用し、端をワイヤーで閉じたところに寄生容量やインダクタンスが形成され、細断の発生に影響を与えたと考えられます。

結論

一般に、さまざまなプリミティブでクロック信号を生成することができました。また、Kintex-7を例として使用すると、プリミティブの位置によってレイテンシが異なることもわかりました。私自身に代わって、実行した実験が完全に正しいとは考えていません。たとえば、カウンターのビット幅が計算されなかった、さまざまなクロックドメインからの信号転送が考慮されなかった(ただし、バッファー内の信号を数クロック保持したが)、ChipScope自体を削除し、別の方法を見つける必要がある生成された周波数を分析します。

発生した問題:

Vivado ISE , . :

- set_property ALLOW_COMBINATORIAL_LOOPS TRUE [get_nets -of_objects [get_cells gen_clk_inst/LUT1_inst]]

- NET «s1» CLOCK_DEDICATED_ROUTE = FALSE;