MOS構造が引き続き機能し、大幅に削減されていることは注目に値しますが、ほとんどのものはそのように削減することはできません。たとえば、モーターを10倍にスケーリングして、動作することを期待することはできません。ほとんどの物理的なオブジェクトは、スクエアキューブの法則に苦しんでいます:オブジェクトの領域は線形サイズの正方形として成長し、そのボリュームはキューブとして成長します。ただし、MOS構造の場合、スケーリング時のほとんどのコンポーネントは変更されないか、改善されます(たとえば、周波数や電力消費)。スケーリングの詳細については、Mead andConwayの著書「IntroductiontoVLSISystems」を参照してください。..。皮肉なことに、1978年の本は、物質の物理的特性により、スケーリングにはチャネル長に基本的な1/4ミクロン(250 nm)の制限があると主張しています。この制限には非常に欠陥があることが判明しました。FinFETなどのテクノロジーのおかげで、トランジスタは5nmの特徴的なサイズに移行しています。

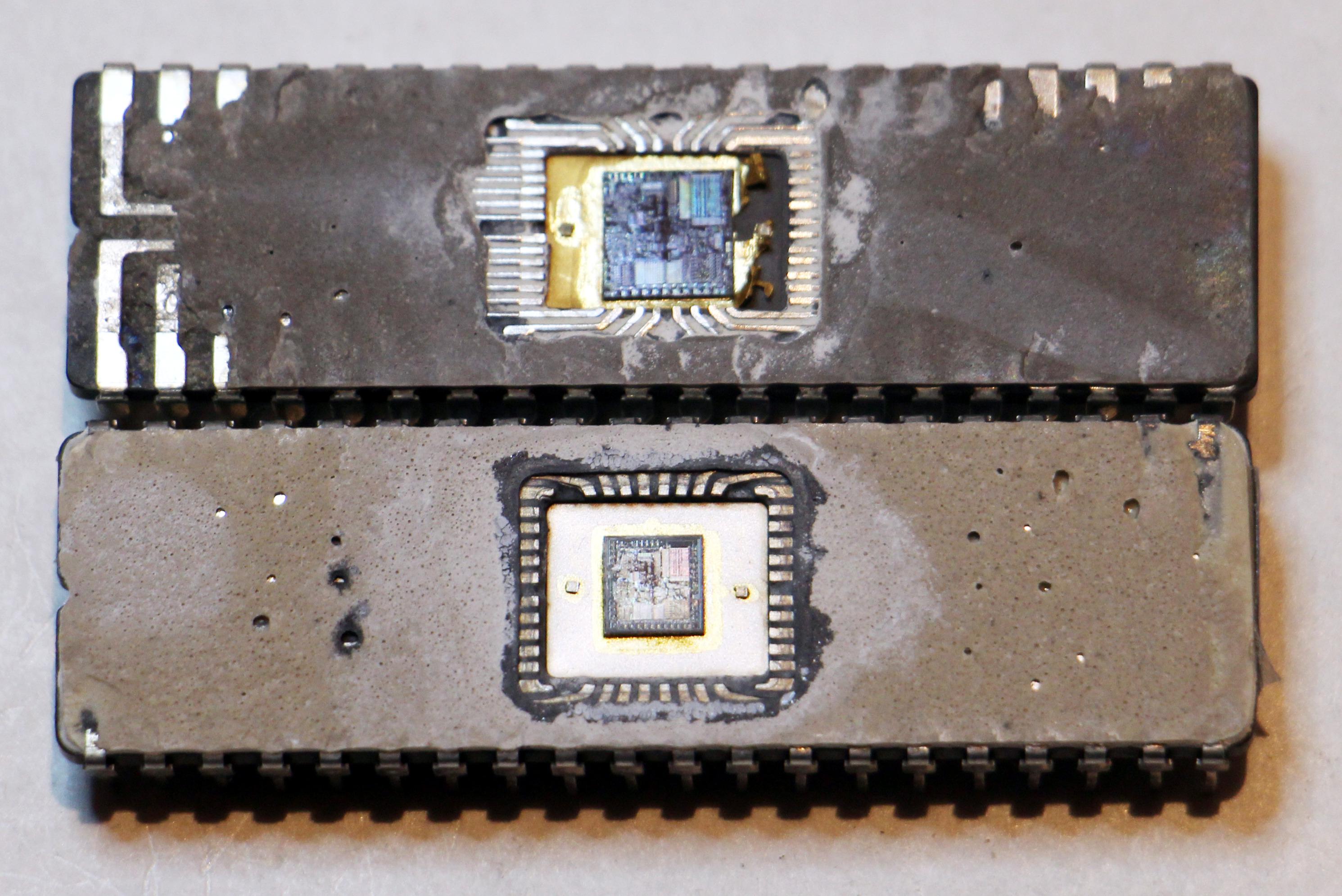

下の写真は、1979年の8086チップと、1986年の明らかに小さいダイを備えたバージョンを示しています。結晶が見えるように、チップからセラミックカバーを取り外しました。更新された8086では、内部回路の長さが元の回路と比較して64%短縮されたため、元の領域の40%を占めています。結晶自体は大幅に減少していません。元の面積の54%を占めています。プロセッサーのハウジングは変更されていません。DIPは40ピンですが、マイクロプロセッサーによく使用されます。

古いチップには、ケースに'78、'79、クリスタルに1979と記載されており、日付コードは下部に7947(1979年の第47週)です。 1978年は新しいチップのケースに書かれ、1986年はクリスタルに書かれています。日付コードはありません。したがって、1986年かそれより少し後に製造する必要があります。ケースの新しいチップの日付が古い理由は明らかではありません。

2つの8086チップの比較。新しいチップの底面のダイははるかに小さくなっています。右上隅の長方形はマイクロコードROMです。

8086は、これまでに製造された中で最も影響力のあるチップの1つです。それは、デスクトップコンピュータとサーバーコンピュータの両方を依然として支配しているx86アーキテクチャの始まりを示しました。最新のCMOSプロセッサとは異なり、8086は6502、Z-80、その他の初期のプロセッサなどのN-MOSトランジスタ上に構築されていました。最初のチップは、Intelがこのプロセスと呼んだように、HMOSテクノロジーを使用して作成されました。 79年に、Intelはその高度なバージョンであるHMOS-IIを発表し、82年には、2つのチップのうち新しいものを作成するために使用されたプロセスであるHMOS-IIIに切り替えました。 HMOSの連続するバージョンごとに、チップコンポーネントのサイズが縮小され、効率が向上します。

NチャネルMOSFETは、特定のタイプのMOSFETです。それらの効率は、Intel 4004などの初期のマイクロプロセッサで使用されているPチャネルMOS構造の効率よりもはるかに優れています。最新のプロセッサは、NチャネルトランジスタとPチャネルトランジスタを一緒に使用して電力消費を削減します。これはCMOSと呼ばれます。..。 NチャネルMOSFETで構成されたゲートには、トランジスタであるプルアップ抵抗が必要です。枯渇負荷トランジスタは、1970年代半ばに導入されたトランジスタの一種です。このタイプのトランジスタは、プルアップ抵抗の役割に適しているため、追加の電源電圧は必要ありません。最後に、MOSFETは元々金属を使用してゲートを作成していました(MOSFETの文字M)。しかし、1960年代後半、フェアチャイルドは金属に代わるポリシリコンを開発しました。その結果、チップはより効率的で製造が容易になります。その結果、1960年代後半から1970年代半ばにかけて、MOS構造の製造にいくつかの根本的な変化が起こり、6502、Z-80、8085、8086およびその他の初期のプロセッサが成功しました。 1980年代には、CMOSプロセッサがより高速で、消費電力が少ないために引き継がれました。

不思議なことに、HMOSの頭文字のHが正確に何を表しているのかは完全には明らかではありません。この頭字語の写しをIntelから見つけていません。スペックは言う「インテルの高度なシリコンNチャネルHMOSのゲートはプロセスを製造する」または「HMOSは非常に効率的nチャネルMOSプロセスです。」 Intelは後に、 CHMOSを補完的な高速金属酸化物半導体[補完的な高速金属酸化物半導体]として説明しました。 Motorolaは、HMOSを高密度MOSとして識別しました。他の情報源は、それを高速MOSまたは短いチャネルの高密度MOSとして説明しています。 Intelには特許があります「MOSプロセスと高密度高速デバイス」に変換されるので、おそらくHは「高密度」と「高速」の両方を表します。

興味深いことに、Intelは4K静的RAMを使用して、マイクロプロセッサやその他のチップのプロセスを使用する前に、各HMOSプロセスを開発しました。彼女はRAMチップを使用しましたが、これはおそらく回路が非常に密集しているためですが、同じメモリセルが何度も繰り返されるため、設計は比較的簡単です。彼女はすべての回路レイアウトルールを開発した後、はるかに複雑なプロセッサの構築を開始することができました。

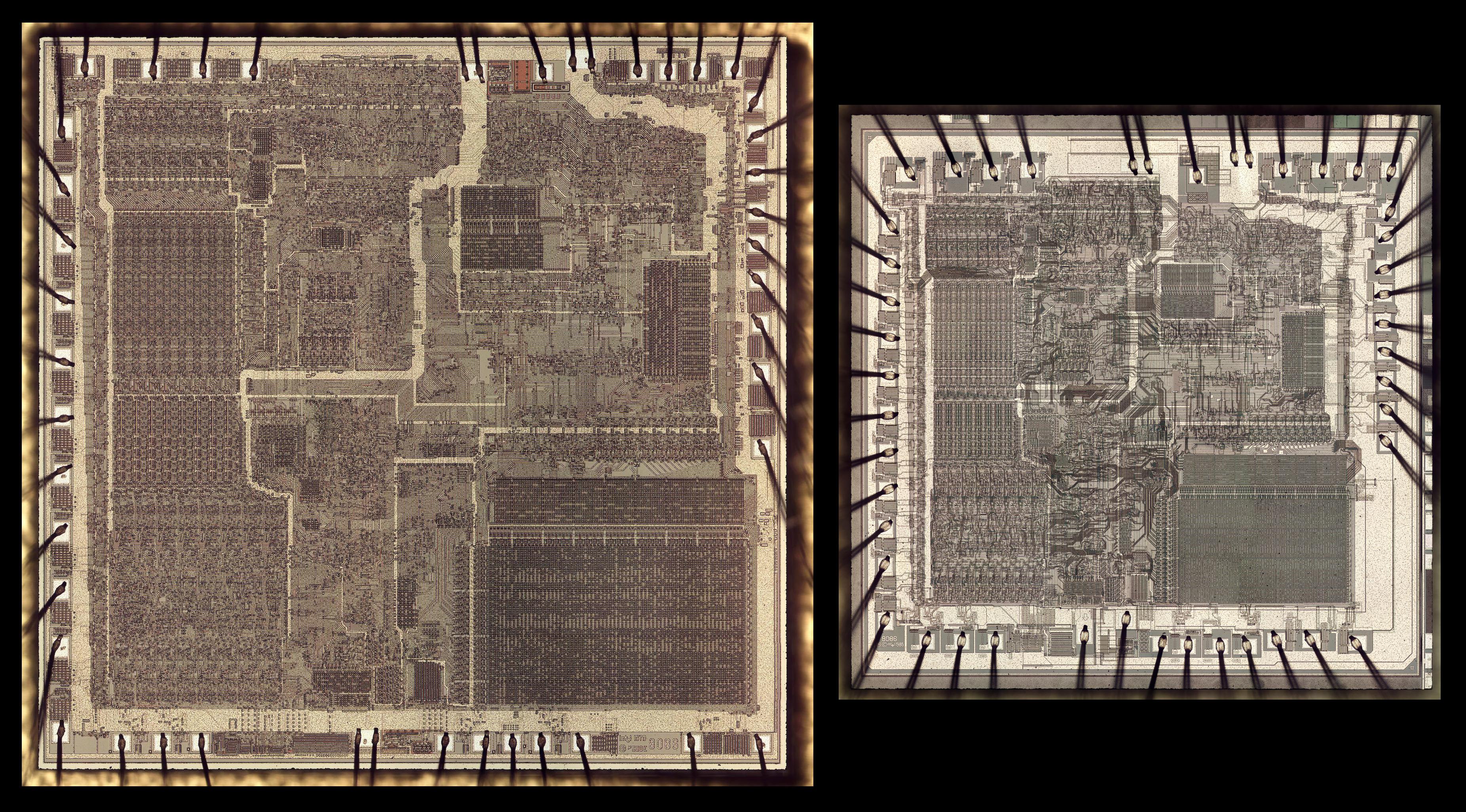

同じスケールの8086クリスタルの2つのバージョン。入ってくる導体は、結晶の周囲にあるパッドに接続されています。

上の写真は、同じスケールの8086クリスタルの2つのバージョンを示しています。 2つのチップは、一見異なるように見えるかもしれませんが、内部のコンポーネントのレイアウトは同じです。真ん中の右側のチップには、左側のチップにはない暗い線がたくさんありますが、これは単なる射撃のアーティファクトです。これらの線は、金属の下にあるポリペプチドの層です。クリスタルの左側では、すべての導体が同じように配置されていますが、写真では非常に薄いです。新しいチップは金属層が薄いので、ポリシリコンの方が見やすくなっていると思います。

2つのチップの高解像度写真を拡大縮小して比較したところ、わずかな違いを除いて、チップの主要部分は完全に同じであることがわかりました。唯一の問題は、マイクロコードに変更があったかどうかです。外から見ると同じように見えますが、少しずつ比較していません。

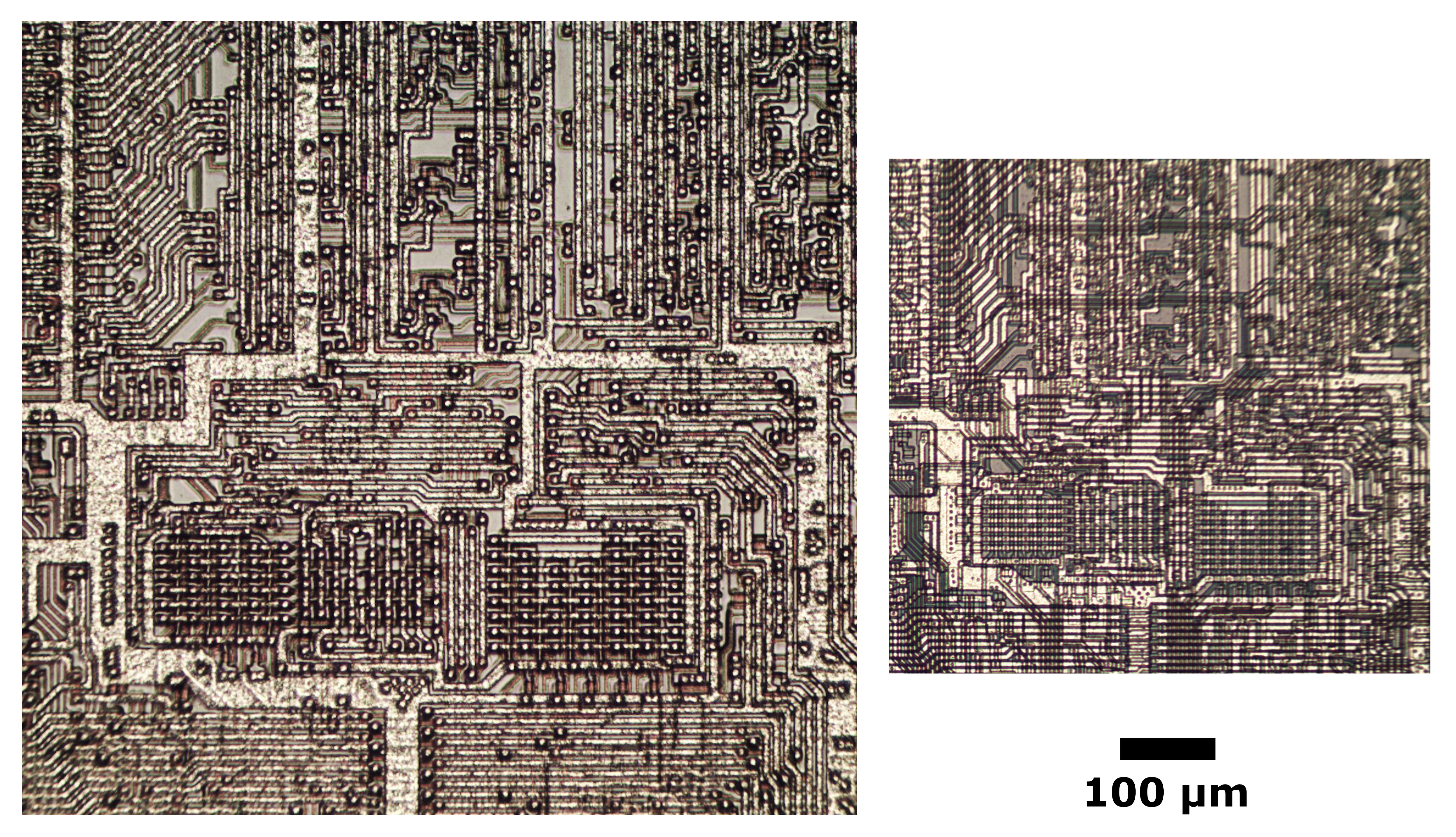

下の拡大写真は、2つの結晶の同一の鎖を示しています。コンポーネント間の正確な対応を確認できます。これは、回路のサイズが縮小されただけで、やり直されていないことを示しています。写真では、金属層がチップの上にあります。右の写真はいくつかのポリペプチドを示しています。

同じスケールで、2つの異なるチップ上の同じプロット

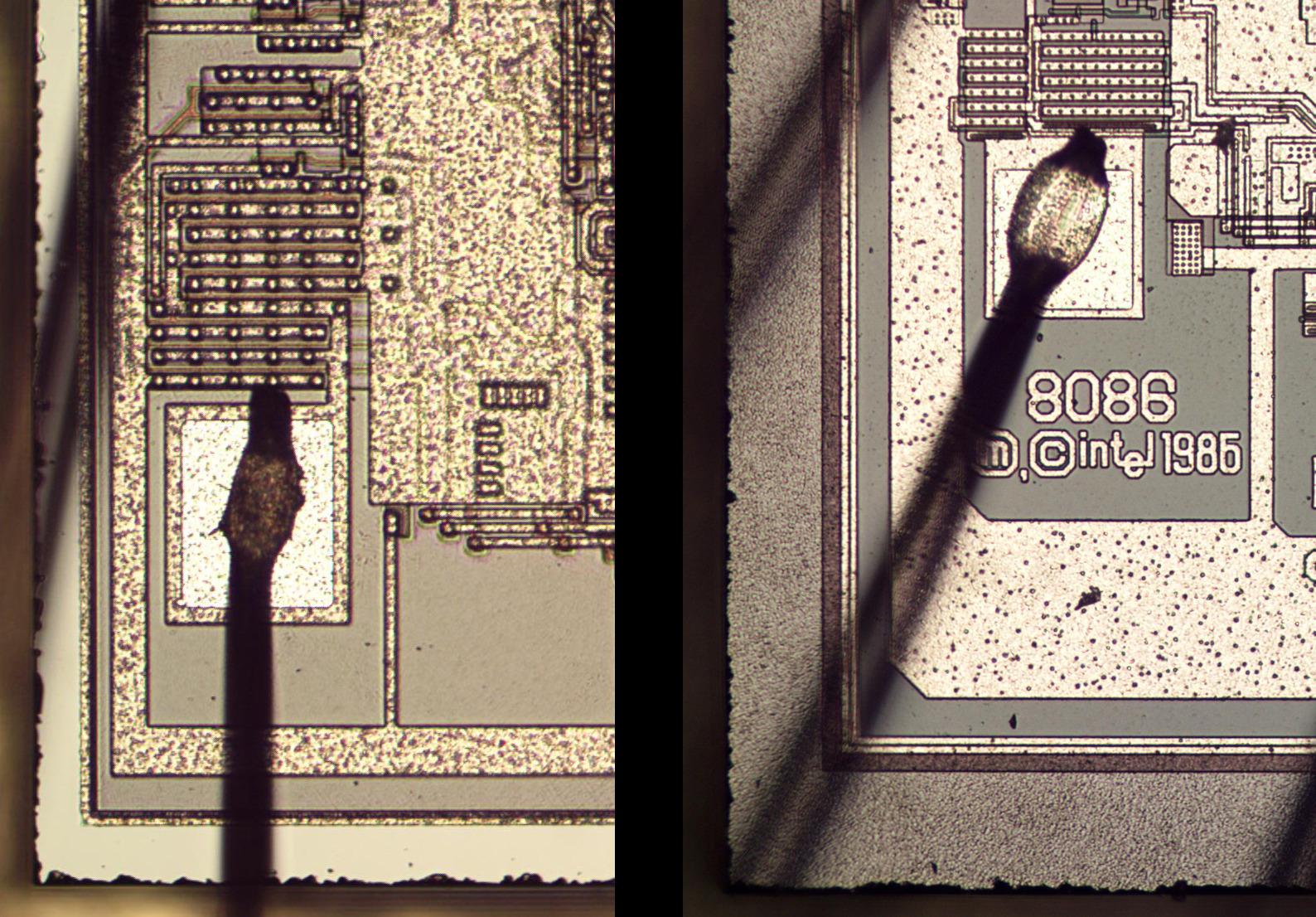

しかし、結晶の周囲に沿って、違いは重要です。接触パッドは、特に右下で互いに接近しています。これには2つの理由があります。まず、コンタクトパッドは接続ワイヤに接続する必要があるため、大幅に減らすことはできません。次に、必要な電流を維持するために、電力分配トラックの端が広くなっています。たとえば、写真の右下、マイクロコードRAMの右側を見てください。特に、これは、回路の中央の電力トレースが他のすべてと一緒に縮小されるために行われます。したがって、外側のトレースはこれらの損失を補償する必要があります。さらに、新しいチップの薄い金属層は、膨張しない限り同じ電流をサポートできません。

古いチップ(左)と新しいチップ(右)のコンタクトパッドと関連するトランジスタ。著作権日付の数字「6」の上部は異常にフラットです。「5」が「6」に修正されているようです。

上の写真は、ジャンパー線がはんだ付けされたパッドを示しています。トランジスタはパッドの上にあります。新しいチップの場所はほぼ同じサイズですが、トランジスタは小型化され、再設計されています。新しいチップのはるかに厚い金属導体に注意してください。おそらく空き容量があったため、Intelのロゴが右から左に移動しました。

結晶を詳しく見てみましょう

まず、8086およびその時代の他のチップで使用されたnチャネルMOSの製造の小さな歴史。これらのチップは、ヒ素またはホウ素の不純物を添加してトランジスタを形成したシリコン基板で構成されていました。上部のポリシリコンの層は、トランジスタのゲートを作成し、コンポーネントを導体に接続することを可能にします。最後に、上部の1つの金属層がすべてのコンポーネントを結合します。

半導体製造プロセス(たとえば、HMOS-III)には、コンポーネント(シリコン、ポリシリコン、および金属層)間の最小サイズと距離に関する特定の規則があります。チップを詳しく見ると、HMOSIとHMOSIIIでこれらのパラメーターがどのように異なっているかがわかります。プレート(HMOSIIIテクノロジーから取得))さまざまなHMOSプロセスの特性を要約しました。バージョンごとに、特徴的なサイズが小さくなり、パフォーマンスが向上しました。HMOS-IIからHMOS-IIIへの移行において、Intelは40%のパフォーマンス向上を達成しました。

| HMOS I | HMOS II | HMOS III | |

|---|---|---|---|

| 拡散ステップ(µ) | 8.0 | 6.4 | 5.0 |

| ポリシリコンピッチ(µ) | 7.0 | 5.6 | 4.0 4.0 |

| 金属ステップ(µ) | 11.0 | 8.0 | 6.4 |

| バルブ酸化物の厚さ(Å) | 700 | 400 | 250 |

| チャネル長(µ) | 3.0 3.0 | 2.0 | 1.5 |

| Idsat(mA) | 8.0 | 14.0 | 27.0 |

| 最小バルブ遅延(ps) | 1000 | 400 | 200 |

| 放熱弁遅延(pJ) | 1.0 | 0.5 | 0.25 |

| 線形削減率 | 1.0 | 0.8 | 0.64 |

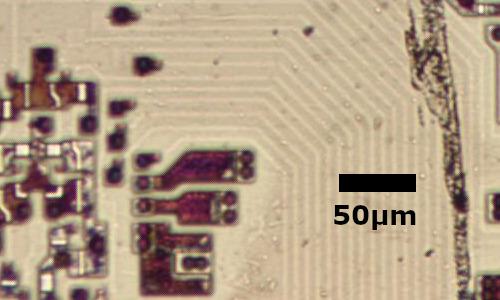

下の写真は顕微鏡で撮影したもので、古い8086チップのトランジスタの複雑な配置を示しています。暗い領域は不純物を含むシリコンであり、明るい長方形はトランジスタゲートです。写真は約21個のトランジスタを示しています。重要な寸法は、チャネルの長さ、つまりソースからドレインまでのバルブの長さです(これは明るい長方形の小さい方の辺です)。これらについて、私は3 µmで長さを測定しました。これは、HMOS Iの公開された仕様に一致しています。これは、チップが3 µmプロセス技術を使用して製造されたことを示します。比較のために、今日のプロセッサは600分の1の5nmに切り替えています。

写真の3つのトランジスタのゲートがはるかに大きいことに気づいたかもしれません。これらのトランジスタは、NMOSに典型的なプルアップ抵抗として動作します。サイズを大きくするとトランジスタが弱くなるため、プルアップ電流が弱くなります。

8086. . – , .

下の写真は、同じスケールの新しい8086のトランジスタを示しています。トランジスタのサイズはすでにはるかに小さいことがわかります。直線寸法は元の64%であるため、トランジスタは以前のものと比較して面積の40%を占めます。私はこの結晶を別の方法で処理したので、ポリペプチドが残っていました-これらは黄色がかった線です。不純物のあるシリコンはピンクがかったように見え、前の写真よりも見えにくくなっています。バルブの長さを1.9ミクロンと決定しました。これは、前の3ミクロンの64%です。 HMOS-IIIは1.5µmの大幅に短いチャネル長を維持しますが、すべてが同じ回数だけ短縮されるため、チャネル長は必要以上に長くなることに注意してください。これは、均一に減少すると、新しいプロセスの特定の利点が失われることを示していますが、これははるかに簡単です。新しいチップを最初から設計するよりも。

新しい8086チップのトランジスタ。シリコンまたはポリシリコンと金属層(ここで削除)の間には多くの貫通ワイヤがあります。

また、金属層のタイヤ間のピッチも調べました。下の写真は、古いチップの水平および垂直の金属導体を示しています。金属タイヤのピッチを11ミクロンと決定しました。これは、HMOS Iの公開されている特性と一致します。HMOSIIIプロセスも6.4ミクロンをサポートしていましたが、64%に減らすと、新しいチップで7ミクロンのステップになります。以前と同様に、同じ削減係数により、新しいプロセスのすべてのメリットを享受できなくなります。

古い8086チップの金属層。金属の下に赤みがかったポリシリコン導体が見えます。

最後に、ポリシリコン導体のピッチを調べました。下の写真は古い8086を示しています。ポリシリコンが除去され、かすかな白い線だけが表示されます。これらの平行なポリペプチドラインは、チップのある部分から別の部分に信号を送信するバスを形成した可能性があります。ポリシリコンの場合、ドキュメントと一致する7ミクロンのステップを測定しました。興味深いことに、HMOSの特性により、ポリシリコン導体は金属導体よりも密集させることができます。新しいチップのピッチは4.5ミクロンですが、サイズを4ミクロンにすることもできます。

古い8086チップ上のポリシリコントラック

結論。

クリスタルをスケーリングすることで、ゼロからの設計に労力を費やすことなく、プロセッサーの速度を上げてコストを削減することができます。ただし、2つのチップを比較すると、ダイのスケーリングは、単にダイ全体を縮小するよりも複雑なプロセスであることがわかります。ほとんどの回路は収縮するだけですが、パッドは他のパッドほど収縮しないため、再配置する必要があります。電力配分も変更され、チップの周囲に電力導体が追加されました。

最新のマイクロプロセッサは、依然として結晶スケーリング技術を使用しています。2007年、Intelはティックタックモデルに切り替えました。このモデルでは、既存のチップ(ティック)のスケーリングが新しいマイクロアーキテクチャ(「タック」)のリリースと交互に行われます。

参照: